GF Galileo SMA S.r.l.

- SPACE DIVISION -

**HASI**

HASI-SP-OG-004 ISSUE:7 Sep 95

10/95

ISSUE:7 Sep 95 Page: 1 of 204

16/192.2.1

Document Type: SPECIFICATION

HASI DPU SOFTWARE

**USER REQUIREMENTS DOCUMENT**

Prepared by: Department: Signature: Date: M. COSI DIOS/732 F. POSSANZINI DIOS/736 Checked by: Department: Signature: Date: M. COSI DIOS/732 Approved by: Department: ignature: Date: **A. TROTTA** DAQ/SW169 Authorized by: Department: Signature: Date:

DIOS/730

R. DE VIDI

GF Galileo SMA S.r.l.

- SPACE DIVISION -

## **HASI**

HASI-SP-OG-004 ISSUE:7 Sep 95 Page: 2 of 204

## DOCUMENT CHANGE RECORD

| ISSUE      | DATE         | TOTAL<br>PAGES | PAGES<br>AFFECTED                    | DESCRIPTION OF MODIFICATIONS                                                                                       |

|------------|--------------|----------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| l<br>Draft | Oct 91       |                | ALL                                  | General description                                                                                                |

| 2<br>Draft | Nov 91       |                | ALL                                  | Small changes                                                                                                      |

| 3<br>Draft | May 92       |                |                                      | Changes after EPDR                                                                                                 |

| 4<br>Draft | May 93       |                | ALL                                  | First draft version after DELTA EPDR of 1/2 March 1993                                                             |

| 5<br>Draft | June 93      |                |                                      | Added OP MODES definition. Added HW I/F spec. (draft); PPI req. still missing                                      |

| 6<br>Draft | 02/07/93     |                |                                      | Lat Draft Issue before freezing of version 1.0                                                                     |

| 7<br>Draft | 14/10/93     |                |                                      | Updated after PARIS Meeting of 8-9 July 1993.                                                                      |

| 1          | 07/10/93     |                | ALL                                  | Updated after Progress Meeting in OG sept. 1994                                                                    |

| 2          | 20/09/94     |                |                                      | OG Working copy - red line copy of Issue                                                                           |

| 3          | Oct 94       |                |                                      | OG Working copy - red line copy of Issue<br>2                                                                      |

| 4          | 14/12/94     | 225            | ALL                                  | Updated for memory size optimization and for add RAE requirements; ACC, PPI and PWA req. changes agreed with CO'Is |

| 5          | 03/01/95     | 210            | ALL                                  | Updated after Meeting held in Padua the 15/12/94; the modifications are agreed with PI.                            |

| 6          | 01/06/95     | 201            | SOME                                 | Update after CDR (March 95) and system test.                                                                       |

| 7          | 30/09/95     |                | 18,34,35,<br>130,142-147             | EEPROM override capability.                                                                                        |

|            |              |                | 29,50,124,136<br>,137                | Entry worst_case.                                                                                                  |

|            |              |                | 5 3 , 1 1 3 ,<br>182,184-189         | Typewriter errors.                                                                                                 |

|            |              |                | 55,57-59,<br>125,133,<br>176,179-181 | Software testing.                                                                                                  |

|            |              |                | 60,61,64,65                          | PROM default values.                                                                                               |

|            |              |                |                                      |                                                                                                                    |

|            |              |                |                                      |                                                                                                                    |

|            | <del> </del> |                |                                      |                                                                                                                    |

## **HASI**

HASI-SP-OG-004 ISSUE:7 Sep 95 Page: 3 of 204

# LIST OF VALID PAGES

| Page | Issue<br>n. | Page | Issue<br>n. | Page | Issue<br>n. | Page | Issue<br>n. | Page | Issue n. |

|------|-------------|------|-------------|------|-------------|------|-------------|------|----------|

| 1    | 7           | 26   | 4           | 51   | 6           | 76   | 4           | 101  | 5        |

| 2    | 7           | 27   | 4           | 52   | 7           | 77   | 4           | 102  | 4        |

| 3    | 7           | 28   | L           | 53   | 7           | 78   | 4           | 103  | 4        |

| 4    | 7           | 29   | 7           | 54   | 6           | 79   | 4           | 104  | 4        |

| 5    | 4           | 30   | 6           | 55   | 7           | 80   | 4           | 105  | 4        |

| 6    | 4           | 31   | 6           | 56   | 4           | 81   | 4           | 106  | 6        |

| 7    | 4           | 32   | 6           | 57   | 7           | 82   | 6           | 107  | 6        |

| 8    | 5           | 33   | 5           | 58   | 7           | 83   | 4           | 108  | 7        |

| 9    | 4           | 34   | 7           | 59   | 7           | 84   | 4           | 109  | 7        |

| 10   | 5           | 35   | 7           | 60   | 7           | 85   | 4           | 110  | 4        |

| 11   | 6           | 36   | 6           | 61   | 7           | 86   | 4           | 111  | 6        |

| 12   | _4          | 37   | 6           | 62   | 6           | 87   | 4           | 112  | 6        |

| 13   | 4           | 38   | 6           | 63   | 5           | 88   | 4           | 113  | 7        |

| 14   | 4           | 39   | 6           | 64   | 7           | 89   | 6           | 114  | 6        |

| 15   | 6           | 40   | 6           | 65   | 7           | 90   | 6           | 115  | 6        |

| 16   | 4           | 41   | 6           | 66   | 6           | 91   | 4           | 116  | 4        |

| 17   | 4           | 42   | 6           | 67   | 6           | 92   | 4           | 117  | 6        |

| 18   | 7           | 43   | 6           | 68   | 6           | 93   | 4           | 118  | 4        |

| 19   | 6           | 44   | 6           | 69   | 4           | 94   | 4           | 119  | 5        |

| 20   | 4           | 45   | 6           | 70   | 4           | 95   | 4           | 120  | 6        |

| 21   | 4           | 46   | 4           | 71   | 4           | 96   | 4           | 121  | 5        |

| 22   | 4           | 47   | 6           | 72   | 4           | 97   | 4           | 122  | 6        |

| 23   | 4           | 48   | 6           | 73   | 4           | 98   | 6           | 123  | 6        |

| 24   | 4           | 49   | 6           | 74   | 4           | 99   | 4           | 124  | 7        |

| 25   | 4           | 50   | 7           | 75   | 4           | 100  | 6           | 125  | 7        |

GF Galileo SMA S.r.l.

- SPACE DIVISION -

**HASI**

HASI-SP-OG-004 ISSUE:7 Sep 95 Page: 4 of 204

| Page | Issue<br>n. | Page | Issue<br>n. | Page | Issue n. | Page | Issue<br>n. | Page | Issue n. |

|------|-------------|------|-------------|------|----------|------|-------------|------|----------|

| 126  | 6           | 151  | 6           | 176  | 7        | 201  | 6           | 226  |          |

| 127  | 6           | 152  | 6           | 177  | 6        | 202  | 7           | 227  |          |

| 128  | 7           | 153  | 6           | 178  | 6        | 203  | 7           | 228  |          |

| 129  | 6           | 154  | 6           | 179  | 7        | 204  | 7           | 229  |          |

| 130  | 7           | 155  | 6           | 180  | 7        | 205  |             | 230  |          |

| 131  | 6           | 156  | 6           | 181  | 7        | 206  |             | 231  |          |

| 132  | 5           | 157  | 6           | 182  | 7        | 207  |             | 232  |          |

| 133  | 7           | 158  | 6           | 183  | 6        | 208  |             | 233  |          |

| 134  | 5           | 159  | 6           | 184  | 7        | 209  |             | 234  |          |

| 135  | 5           | 160  | 6           | 185  | 7        | 210  |             | 235  |          |

| 136  | 7           | 161  | 6           | 186  | 7        | 211  |             | 236  |          |

| 137  | 7           | 162  | 6           | 187  | 7        | 212  |             | 237  |          |

| 138  | 6           | 163  | 6           | 188  | 7        | 213  |             | 238  |          |

| 139  | 6           | 164  | 6           | 189  | 7        | 214  |             | 239  |          |

| 140  | 6           | 165  | 6           | 190  | 6        | 215  |             | 240  |          |

| 141  | 6           | 166  | 6           | 191  | 6        | 216  |             | 241  |          |

| 142  | 7           | 167  | 6           | 192  | 6        | 217  |             | 242  |          |

| 143  | 7           | 168  | 6           | 193  | 6        | 218  |             | 243  |          |

| 144  | 7           | 169  | 6           | 194  | 6        | 219  |             | 244  |          |

| 145  | 7           | 170  | 6           | 195  | 6        | 220  |             | 245  | -        |

| 146  | 7           | 171  | 6           | 196  | 6        | 221  | _           | 246  |          |

| 147  | 7           | 172  | 6           | 197  | 6        | 222  |             | 247  |          |

| 148  | 6           | 173  | 6           | 198  | 6        | 223  |             | 248  | lı       |

| 149  | 6           | 174  | 6           | 199  | 6        | 224  |             | 249  |          |

| 150  | 6           | 175  | 6           | 200  | 6        | 225  |             | 250  |          |

#### TABLE OF CONTENTS

### 1. INTRODUCTION

- 1.1 PURPOSE

- 1.2 SCOPE

- 1.3 DEFINITIONS

- 1.4 REFERENCES

- 1.4.1 APPLICABLE DOCUMENTS

- 1.4.2 REFERENCED DOCUMENTS

- 1.5 OVERVIEW

## 2. GENERAL DESCRIPTION

- 2.1 PRODUCT PERSPECTIVE

- 2.2 USER CHARACTERISTICS

- 2.3 GENERAL CONSTRAINTS

- 2.4 ASSUMPTIONS AND DEPENDENCIES

- 2.5 OPERATIONAL ENVIRONMENT

## 3. SPECIFIC REQUIREMENTS

## 3.1 CAPABILITY REQUIREMENTS

- 3.1.1 MISSION DEFINITION

- 3.1.2 HASI-DPU-SW OPERATIVE MODES DEFINITION

- 3.1.3 STARTUP MODE

- 3.1.4 TITAN DESCENT MODE

- 3.1.5 CHECKOUT MODE (checkout procedures)

- 3.1.6 SHUTDOWN MODE

- 3.1.7 TELECOMMANDS MANAGEMENT (special checkout functions)

- 3.1.8 HOUSEKEEPING (periodical functions)

- 3.1.9 DESCENT DATA BROADCAST LIST

- 3.1.10 TELEMETRY DATA MANAGEMENT

- 3.1.11 ACC FUNCTIONAL REQUIREMENTS

- 3.1.12 TEM MANAGEMENT

- 3.1.13 PPI MANAGEMENT

- 3.1.14 PWA MANAGEMENT

- 3.1.15 BOOMS RELEASE (MCA ACTIVATION)

### 3.2 CONSTRAINTS REQUIREMENTS

| - | _  |   |     |

|---|----|---|-----|

| 3 | ٠, | 1 | CPU |

| _ | 4  | 1 | CFU |

- 3.2.1.1 CPU TYPE

- 3.2.1.2 ADDRESSES SPACE updated 23/3/94

- 3.2.1.3 EXTERNAL INTERRUPTS

- 3.2.1.4 EEPROM DEVICE updated 31/3/94

- 3.2.1.5 INTERRUPT CONTROLLER

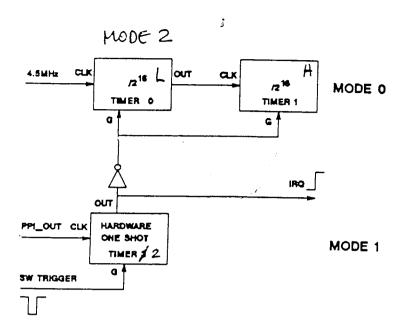

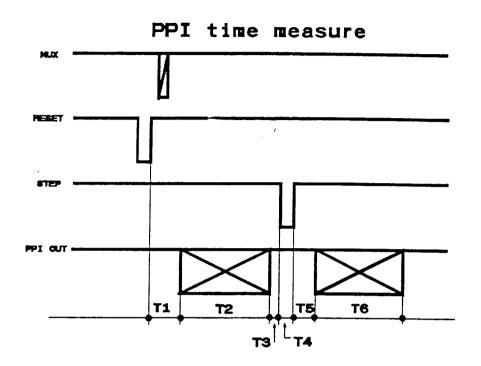

- 3.2.1.6 PROGRAMMABLE TIMERS AND PPI FREQUENCY MEASUREMENT LOGIC updated 23/3/94 updated 31/3/94

- 3.2.1.7 PWA INTERFACE REGISTER

- 3.2.1.8 WATCH DOG LOGIC

- 3.2.1.9 NMI LOGIC

#### 3.2.2 CDMS I/F BOARD

- 3.2.2.1 STATUS WORD

- 3.2.2.2 PACKET TM I/F

- 3.2.2.3 MEMORY LOAD & BCP LINE SELECTION MULTIPLEXER

- 3.2.2.4 MEMORY LOAD I/F updated 23/3/94

- 3.2.2.5 BCP I/F

- 3.2.2.6 VALID I/F

- 3.2.2.7 4 CHANNEL DMA

- 3.2.2.8 MCA INTERFACE

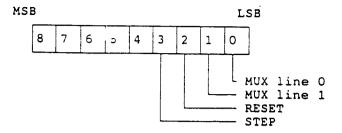

- 3.2.2.9 PPI FREQUENCY CHANNELS SELECTION REGISTER updated 23/3/94

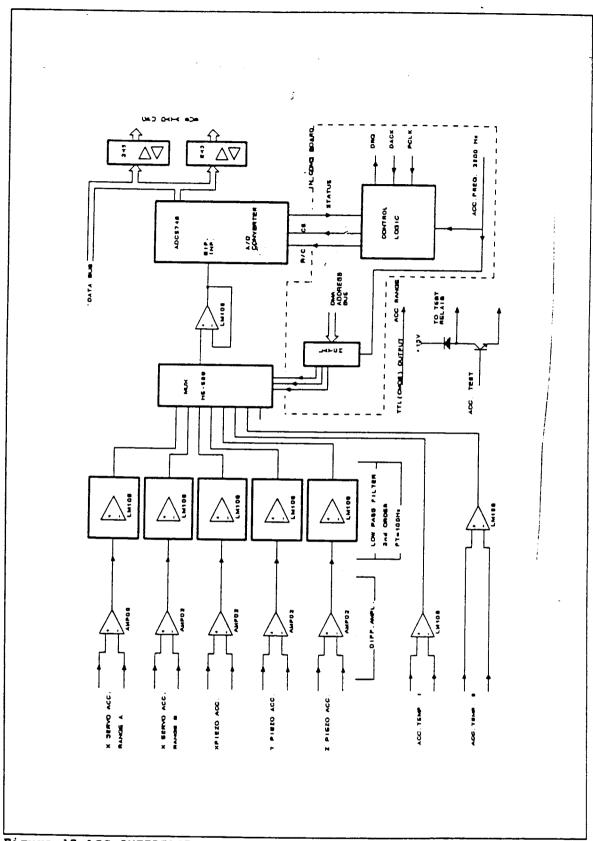

### 3.2.3 ADC CONVERTERS BOARD

- 3.2.3.1 DESCRIPTION

- 3.2.3.2 ADC 1

- 3.2.3.3 ACC XSERVO RANGE SELECTION

- 3.2.3.4 ACC XSERVO TEST SWITCH

- 3.2.3.5 RESOLUTION

- 3.2.3.6 ADC 2 (TEM & HK ADC CHAIN)

3.2.3.7 TEM CURRENT GENERATOR SWITCHING SEQUENCES

3.2.3.8 TEM READING

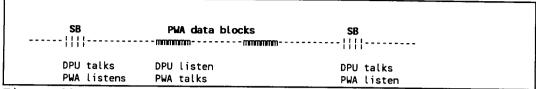

3.2.4 PWA DATA LINK PROTOCOL

3.2.5 SW IN FLIGHT MAINTAINANCE

3.2.5.1 MEMORY UPLOADING

3.2.5.2 MEMORY DUMP

3.2.5.3 PROGRAM PARAMETERS UPLOADING

3.2.5.4 PROGRAM BLOCK UPLOADING

3.2.6 QUALITY REQUIREMENTS

3.2.6.1 STANDARDS & METHODS

3.2.6.2 TOOLS

3.2.6.3 RELIABILITY

APPENDIX A : TBD LIST

ANNEX 1 : INTERFACE DATA SHEET

#### 1. INTRODUCTION

#### 1.1 PURPOSE

The purpose of this document is to specify all the users' requirements for the HASI experiment that are capable of being implemented by DPU on board software.

They include experimenters' requirements (scientific source) as well as system requirements (OG source).

This document is produced during the User Requirements definition phase of the software life cycle defined in ESA PSS-05-0 issue 2. It shall be the basis for the production of HASI-DPU Software Requirements Document.

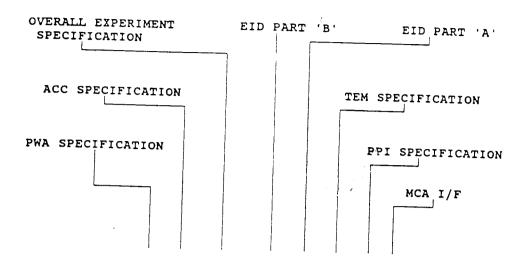

The structure and function breakdown within this document is based on the functions identified for HASI in EID part A and part B documents.

#### 1.2 SCOPE

This document shall be the baseline for all the HASI DPU software activities.

It shall constitute the only reference for the specification of each functionality to be accomplished by HASI-DPU-SW unless expressly specified.

Each applicable user requirement shall be identified by a unique requirement identification label in the form:

URD-<section number>-<requirement number>-<need>

#### where

### 1.3 DEFINITIONS, ACRONYMS and ABBREVIATIONS

HASI : Huygens Atmospheric Structure Instrument

DPU : Data Processing Unit of HASI experiment

HASI-DPU-SW: Hasi experiment on board sw residing on the DPU master

erranne vous seguatement

processor

PPI : Pressure Profile Instrument

TEM : Temperature sensors instrument

PWA : Permittivity and Wave Altimeter

ACC : Accelerometers instrument

CDMS/U : Command and Data Management System/Unit

BCP : Broadcast pulse

OG : Officine Galileo

ESA : European Space Agency

EID : Experiment interface document

URD : (Software) User Requirement Document

PRL : Probe Relay Link

AIV : Assembly and Integration Verification

H/C : Health Check

HK : Housekeeping

SW : Software

HW : Hardware

TM : Telemetry

TC : Telecommand

ML : Memory load

DDBL : Descent Data Broadcast List

MCA : Magnetic Coil Actuator

PIFS : Probe Interface Simulator

ADC : Analog to Digital Converter

EPDH : OG elec. modules only (CPU, A/D, CDMS, DC/DC Conv. and MB)

SB : Status Block Message

C/O : Checkout

CRC : Cyclic Redundance Check

FMI : Finnish Meteorological Institute

RAE : Radar Altimeter Extension

#### 1.4 REFERENCES

#### 1.4.1 APPLICABLE DOCUMENTS

- AD-1 "ESA Software Engineering Standards issue 2" ESA-PSS-05-0 issue 2

- AD-2 "HASI Software Project Plan issue 1" HASI-PL-OG-004

- AD-3 "Huygens EID part A issue 1 rev 3" EID-A

- AD-4 "HASI EID part B Issue 1 rev 1" EID-B

- AD-5 "PWA Specification issue 2" HASI-SP-LPCE-001

- AD-6 "TEM Specification issue 2" HASI-SP-UFT-001

- AD-7 "PPI Specification issue 3" HASI-SP-FMI-001

- AD-8 "ACC Specification issue 2" HASI-SP-UKC-001

- AD-9 MOM HASI-EPDR 3-5 sept 91 OG

- AD-10 MoM HASI-PWA 25/26 sept 91 Gratz

- AD-11 "DBS Specification issue 2" HASI-SP-SSD-001

- AD-12 MoM HASI Design Report 2/3 Dec 91 OG

- AD-13 Mom HASI delta EPDR 2/3 Mar 93 OG

- AD-14 Mom HASI delta EPDR splinter meetings 4 Mar 93

- AD-15 Mom HASI progress meeting (splint) 5/6 May 93

- AD-16 ECR-07: Radar Altimeter

#### 1.4.2 REFERENCED DOCUMENTS

- RD-1 "Huygens system specification issue 02" HUY.AS/c.100.SY.0043

- RD-2 "Huygens PDR system design report issue 01" HUY.AS/c.100.RE.00106

#### 1.5 OVERVIEW

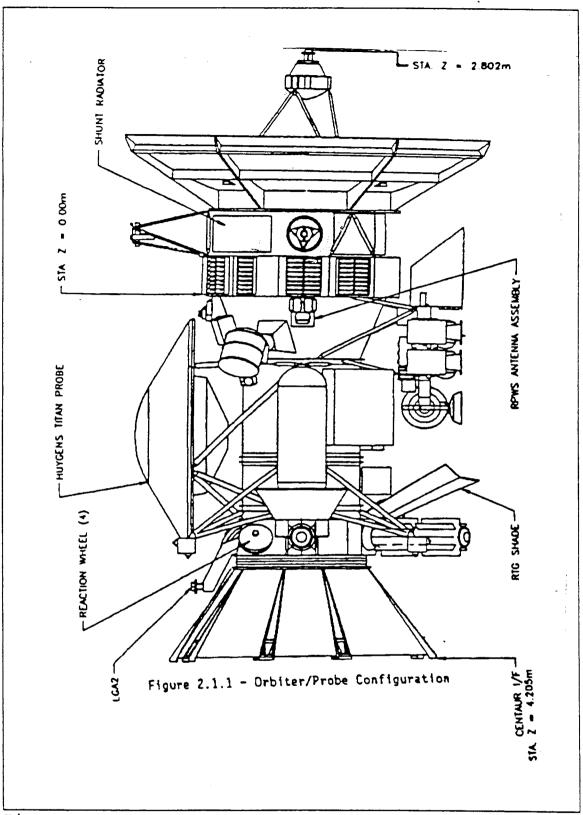

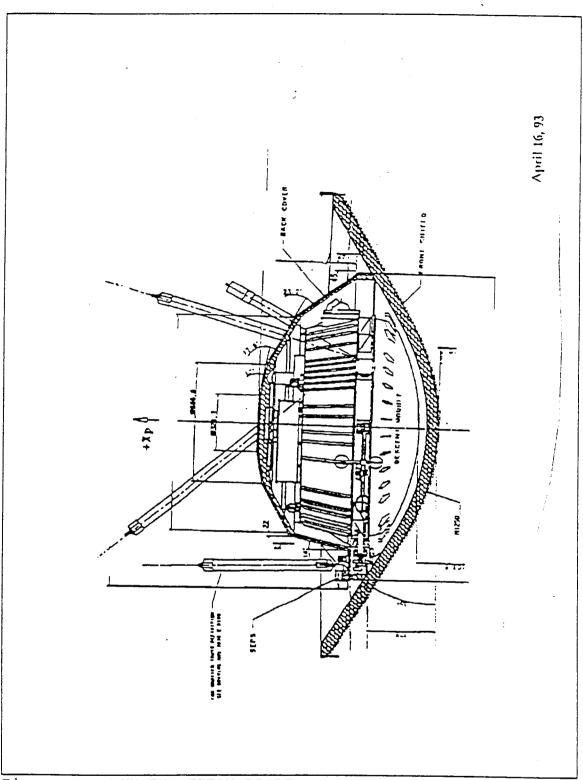

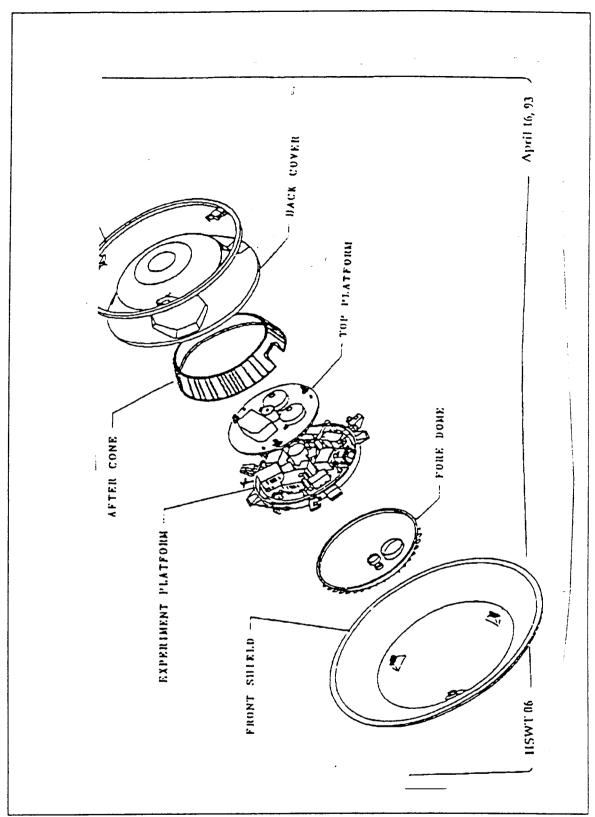

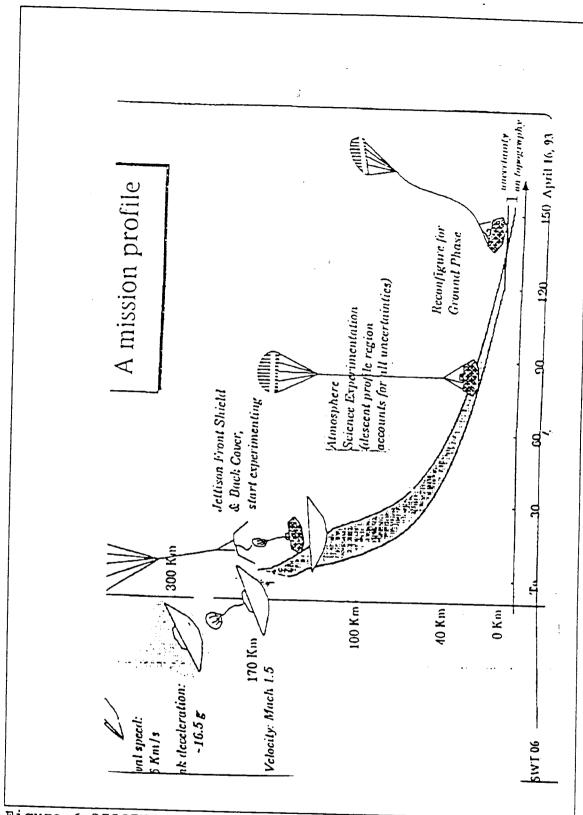

The HASI experiment will lay on experiment platform of the Huygens Titan Probe that is in turn part of the Cassini orbiter (see FIG. 1/2). The Probe consists of a descent module enclosed by a decelerator and an aft cover (see FIG. 3).

The Cassini spacecraft will be launched from Cape Canaveral air Force Station in October 1997; arrival at Saturn will occur in November 2004.

Before Titan encountering, the Probe will be spun up and separated form the Orbiter; Then the Probe will approach and enter the Titan atmosphere. During the Entry in the Titan atmosphere, HASI will achieve its primary scientific objective of the Cassini mission for the study of the Titan atmosphere by means of the acceleration profile yield by ACC sensor data.

After the entry in the Titan atmosphere, at an altitude of approximately 170 Km and a speed of about Mach 1.5, a mortar deploys a drogue parachute that pulls off the aft cover and inflates the main parachute; after a short period the decelerator is separated and falls away. The Descent then continues under the main parachute.

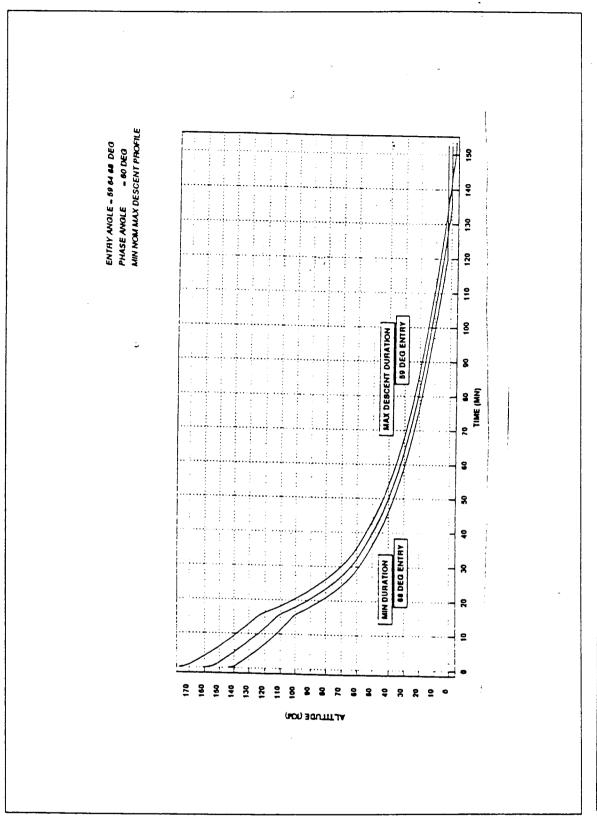

After 15 minutes the main parachute is released and the Probe is stabilized by a small drogue chute as it falls to the surface. Descent profile is shown in fig. 5/6.

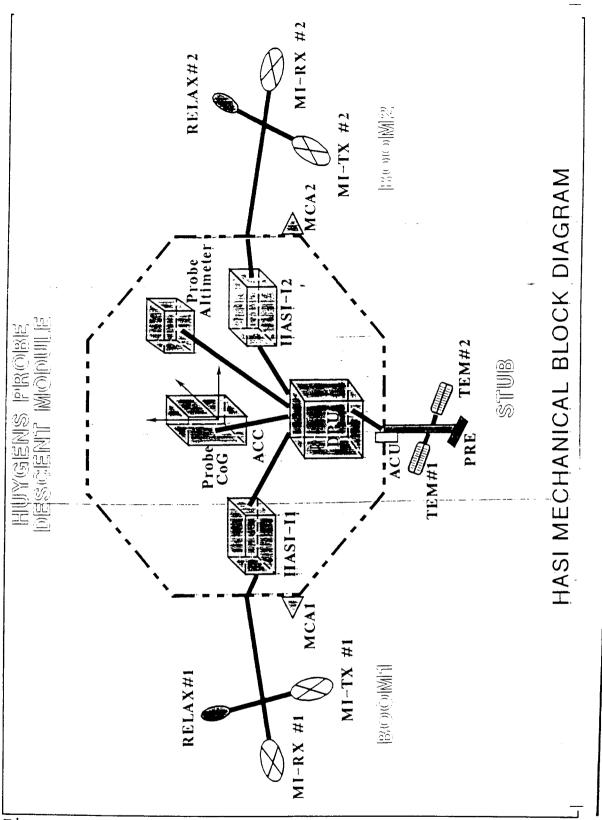

During this descent, by several sensors, ranging from accelerometers and temperature sensors to pressure and electric field sensors, it shall collect and relay back to the Probe CDMS information about the vertical structure of the atmosphere as the Huygens Probe descends. (See FIG. 4)

The HASI operations shall be driven by mission information periodically provided by the Probe CDMS and shall be in accordance a predefined mission programme. It shall operate depending on mission altitude and time as well as on occurring of predefined events.

HASI experiment will return to Probe CDMS telemetry scientific and housekeeping data according to the single experimenters' requirements and to the available Probe Relay Link bit rate.

During CRUISE or GROUND operations HASI activities shall be driven by the Probe CDMS by means of a set of predefined commands able to carry out periodic health check functionality (e.g. sw uploading, device health-checks, calibrations or more complex test session).

Figura 1 : CASSINI ORBITER

Figura 2 : HUYGENS TITAN PROBE

Figura 3 : PROBE SYSTEM CONFIGURATION

Figura 4 : HASI CONFIGURATION

Figura 5 : DESCENT PROFILE

Figura 6 DESCENT PROFILE

#### 2. GENERAL DESCRIPTION

#### 2.1 PRODUCT PERSPECTIVE

#### GENERAL DESCRIPTION

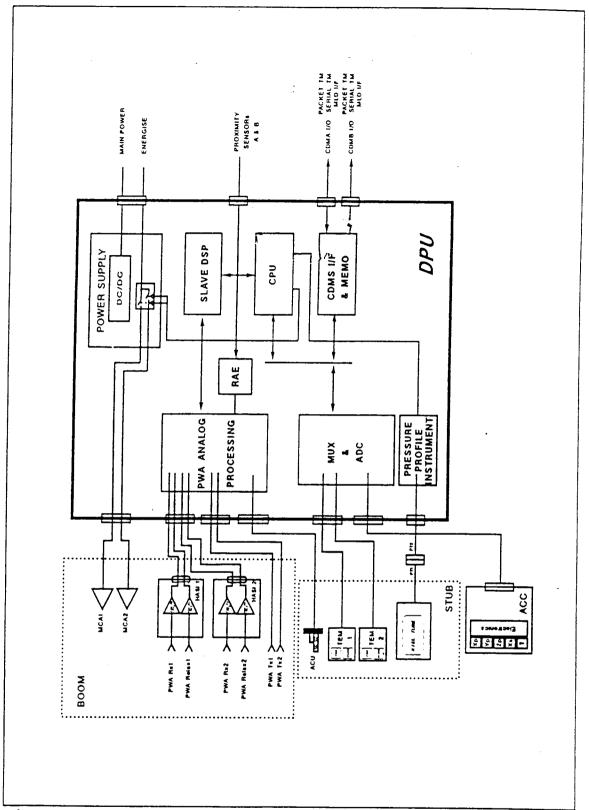

The HASI program flight software is executed by one microprocessor that is part of the DPU.

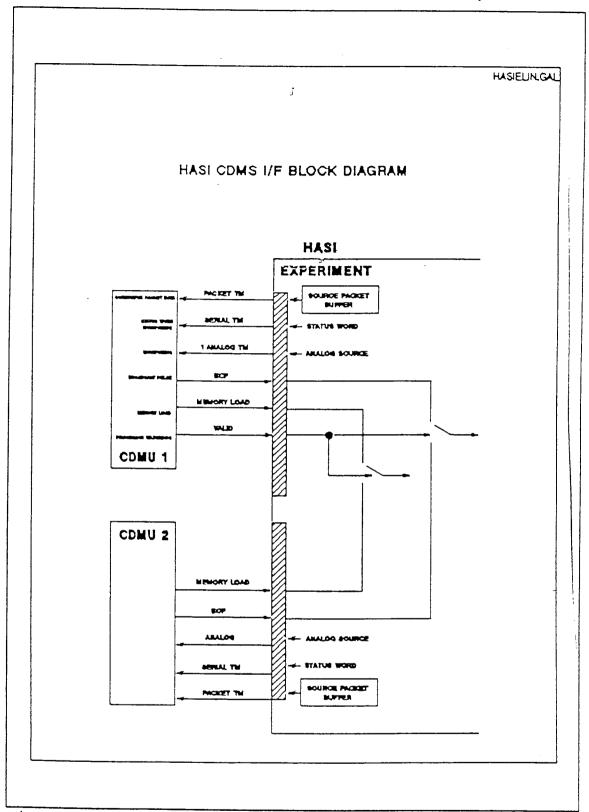

It is linked to the CDMS and collects science data measurements from the connected sensors by means of an ADC converter plus a dedicated interface for pressure data.

A Digital Signal Processor (DSP) performs and controls the measurements and the experiments of the PWA. The DSP is linked to the main processor via a parallel interface; its flight software is considered embedded in the component itself.

The collected science data are transferred to CDMS via ESA Standard Telemetry packets.

#### START UP

After reset (caused by power-on or by unwanted events like SEU) the microprocessor begins its start-up activities that consist of health checks, initialization and warm-up of devices, EEPROM lookup for code or parameters updates which, after an integrity check, shall be loaded in the processor RAM.

To avoid HASI deadlock due to the code parameters loaded into the EEPROM, HASI has the capability to override the EEPROM content itself.

For instance using a combination of DDBL info (SPIN rate value equal to maximum and phase = CHECKOUT), the HASI-DPU-SW skips the EEPROM loading and then, via TC, the EEPROM will be overridden.

The results of these start-up activities shall be reported to CDMS through dedicated TM packets and summarized in the STATUS WORD register.

After successful startup the HASI-DPU-SW shall check the occurring of DDBL packets upon the Memory Load interface.

$\mbox{\it Back-up}$  modes shall be foreseen in order to recovery from start-up failures and DDBL absence.

#### HASI OPERATIONS

The HASI-DPU-SW decides which CDMU channel to use by means of reading the CDMS PROCESSOR VALID line and assessing the correctness of received DDBL packets.

As soon as good DDBL packets are received, the concerning MISSION phase (or operative mode) is entered.

The HASI-DPU-SW shall recognize the operative modes by means of the DDBL information and perform its mission profile according to the broadcasted mission time.

Two operative modes phases shall be recognized by the HASI-DPU-SW: CHECKOUT (i.e. simulated descent) and TITAN DESCENT.

#### TRLECOMMAND OPERATIONS

During the CHECKOUT phases (e.g. simulated descent) HASI may receive telecommands coming from ground via CDMS together with the DDBL messages.

When a Telecommand is received the CHECKOUT FUNCTION is suspended for the time necessary to carry out the pertained Telecommand and report results by means of dedicated Telemetry packets. Upon completion HASI shall restart the suspended function according to the most recent DDBL and shall be ready to execute a new telecommand.

As exception to above written, few special Telecommands are performed in a fraction of time and don't cause CHECKOUT function to be suspended.

Special policies shall be implemented in order to avoid deadlocks of Telecommand operations.

Commandable checkout functions shall comprehend reset of the DPU, health checks, dumping and replacing of DPU memory locations (RAM or EEPROM), dispatching of test commands to the PWA slave processor.

NOTE: The use of Telecommands after LAUNCH shall be restricted to special investigations or recovery actions.

#### ENTRY/DESCENT OPERATIONS

Starting with reception of valid DDBL and mission flag indicating ENTRY/DESCENT and after Tacc (expressed in DDBL time), HASI-DPU-SW shall perform continuous measurements of the Accelerometers.

The measurements shall be stored till 1.5 min after Tdata instant for later transfer to CDMS as the PROBE-ORBITER data link is not available in this time interval.

One minute after the TO instant, according to the "protected energize" time window, the HASI-DPU-SW shall attempt to release the booms devices by means of two repetitions of MCA activation bursts.

After TdataH up to recognition of "proximity of impact" time the micro executes a loop during which accelerometers, temperature, pressure and PWA signals are sampled and on-line processed by peculiar algorithms; the modality of each one changes according to the evolution of the mission time and phases.

When the "proximity of impact" event is recognized by the DPU, the internal accelerometers are gated for the purpose of triggering the real impact instant.

After real impact up to the end of the mission (Tloss) the program keeps on collecting surface measurements and transferring them to CDMS.

Health check results are periodically transmitted to CDMS via Telemetry packets and summarized in the STATUS WORD register.

## 2.2 USER CHARACTERISTICS

## HASI SCIENTIFIC OBJECTIVES

The primary scientific objectives of the Cassini mission for the study of Titan are summarized in the ESA/NASA report on the Phase A study as:

- 1) Determine abundances of atmospheric constituents (including any noble gases); establish isotope ratios for abundant elements; constrain scenarios of formation and evolution of Titan and its atmosphere.

- 2) Observe vertical and horizontal distributions of trace gases; search for more complex organic molecules; investigate energy sources for atmospheric chemistry; model the photochemistry of the stratosphere; study the formation and composition of aerosol.

- 3) Measure winds and global temperatures; investigate cloud physics, general circulation and seasonal effects in Titan's atmosphere; search for lightning discharges.

- 4) Investigate the upper atmosphere, its ionization , and its role as a source of neutral and ionized material for the magnetosphere of Saturn.

The scientific objectives of the Huygens Atmospheric Structure Instrument (HASI) are:

- a) Determine the density pressure and temperature conditions corresponding to the higher part of the atmosphere during the entry phase. Of particular interest is the determination of the physical condition in this region where the "detached" haze, observed by Voyager, is formed.

- b) Measure the stratospheric density, T, P profile of the stratosphere during the descent phase and identify the composition in these layers in terms of trace constituents which condense in this part of the atmosphere. Interpret any data which may suggest the existence of clouds in the upper troposphere.

- c) Measure P,T in the lower troposphere and determine the existence and extent of a convective zone.

- d) Determine (in case of survival after impact), the nature of the surface.

- e) Determine the atmospheric electric conductivity and investigate ionization processes, wave electric fields and atmospheric lightning. Detect acoustic noise due to turbulence and thunders. Characterize electric properties, conductivity and permittivity of the surface material.

- f) Determine the surface large scale and small scale topography, the surface dielectric properties and in particular to be able to remotely distinguish between a liquid or a solid surface before impact. If the surface is liquid information on surface winds may be obtained. All data are measured along the ground track of the descending probe due to horizontal winds during the last 30 Km.

The pressure (PPI), temperature (TEM) sensors and the accelerometers (ACC) address the points (a-d). They will provide the pressure, temperature and density profiles along the path of the Huygens Probe in the Titan atmosphere.

--------- JOHN IMPOLIMENT

The accelerometers will also measure the shock at the impact and in the case of Probe survival the pressure and temperature sensors will give the surface environmental conditions.

The Permittivity and Wave Altimeter (PWA) will address points e) and f).

### 2.3 GENERAL CONSTRAINTS

General constraints affecting the realization of the HASI DPU SW are :

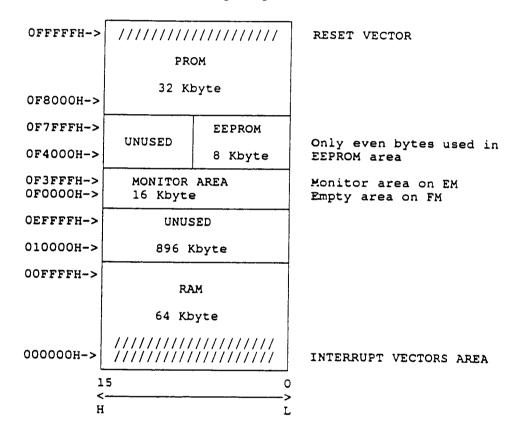

- limited size of memory (32Kb ROM, 64Kb RAM)

- absence of co-processors

- complexity of PROM-EEPROM-RAM program dynamical relocation and self-checking

- complexity of CDMS HW/SW interface

- several sensors HW/SW interfaces

- limited telemetry data rate budget.

## 2.4 ASSUMPTION AND DEPENDENCIES

## SPECIFICATION TREE

HASI DPU SOFTWARE USER REQUIREMENT

#### 2.5 OPERATIONAL ENVIRONMENT

The HASI-DPU-SW shall be a hard constrained real time embedded Software.

Hard deadlines are foreseen for; some functions.

It shall reside on PROMs laying on a microprocessor based electronic board of the HASI DPU box located on the Probe experiment platform (see FIG. 3)

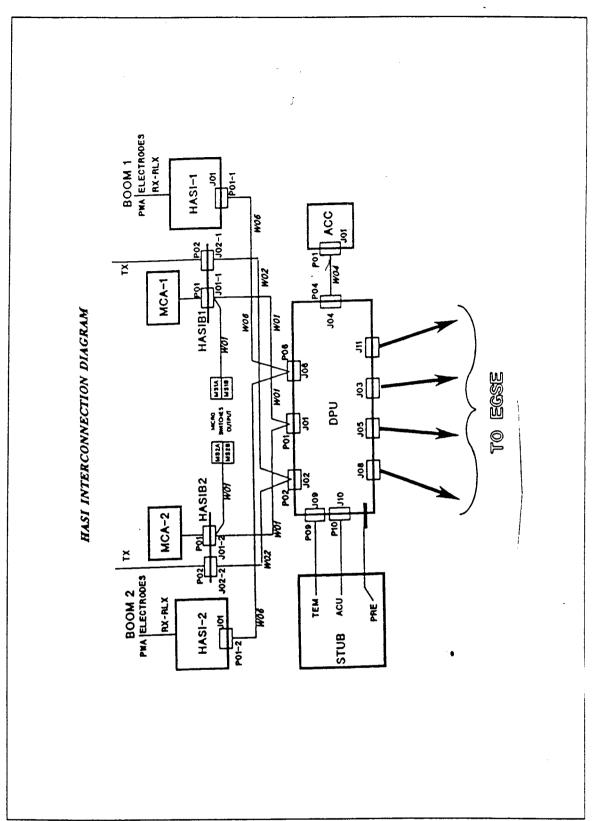

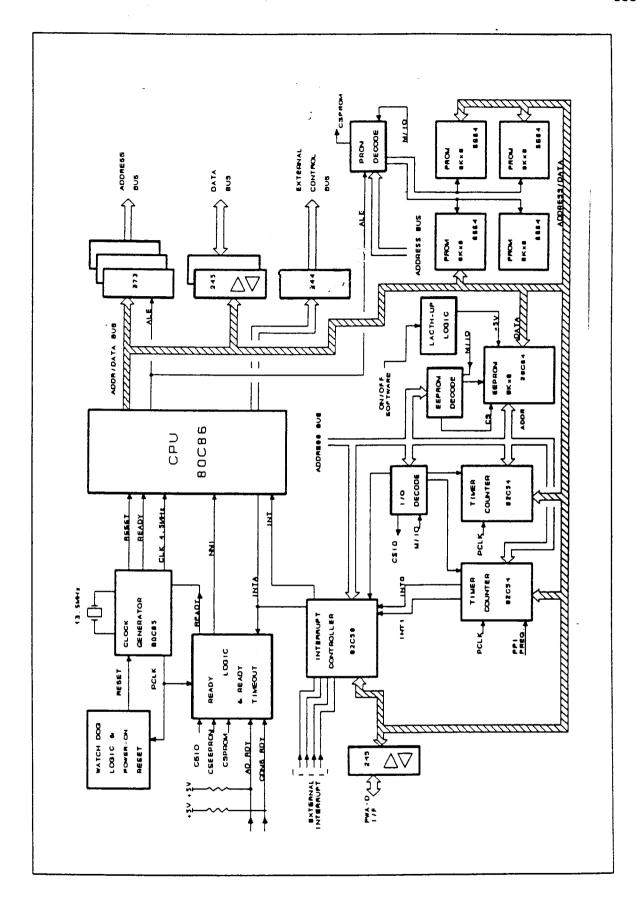

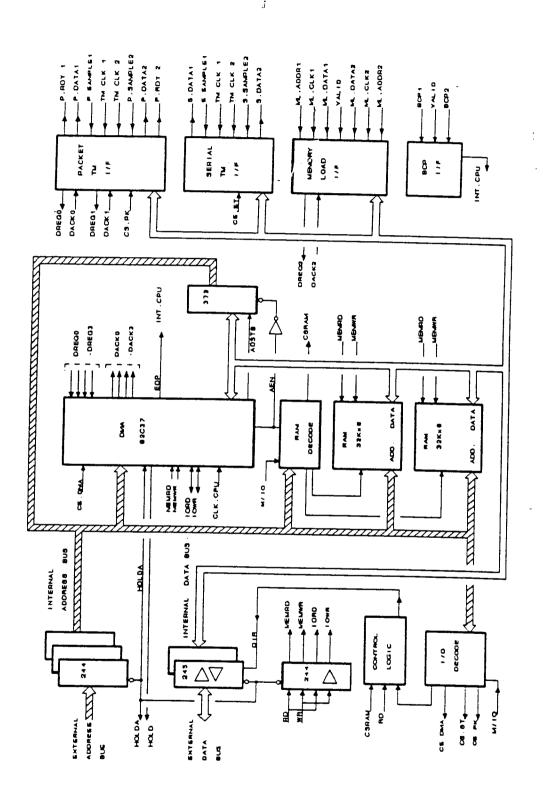

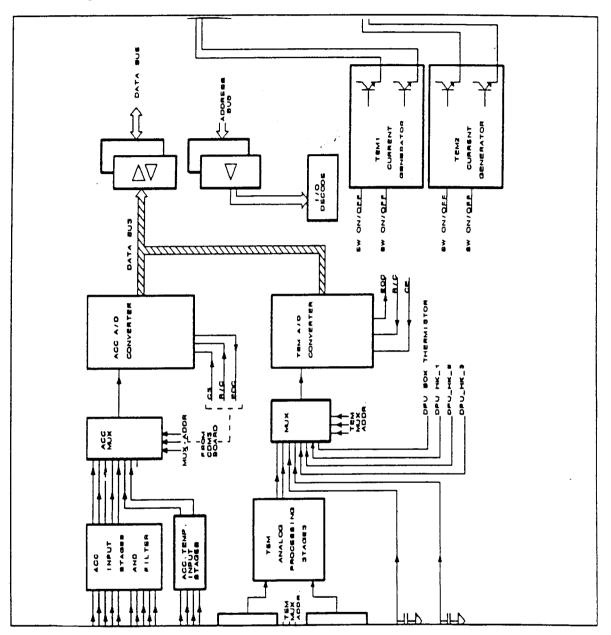

The HASI DPU SW shall interact with the external devices by means of dedicated interface (see FIG.4/7/8/9), they are :

- CDMS interface

- PWA interface

- ACC interface

- PPI interface

- TEM interface

- MCA interface

Figura 7 : HASI FUNCTIONAL DIAGRAM

Figura 8 : HASI INTERCONNECTION BLOCK DIAGRAM

Figura 9 : HASI EXPERIMENT INTERFACE

#### 3. SPECIFIC REQUIREMENTS

#### 3.1 CAPABILITY REQUIREMENTS

#### 3.1.1 MISSION DEFINITION

The HASI mission definition is based upon the Huygens mission that is divided into two major phases.

- PRE-SEPARATION phases (Checkout Operations)

- POST-SEPARATION phases (Titan Mission)

After the HASI AIV is completed and before the Launch, HASI shall be considered in GROUND phase.

The CRUISE phase starts at the Cassini spacecraft earth escape and ends with the Probe Separation from the Orbiter. Its nominal duration is 7 years.

Once approximately each six months during this phase, HASI shall be powered on to execute periodical health-checks and then powered off. These health-checks activities shall be a subset of already carried out GROUND activities.

During the CHECKOUTS phases, the HASI-DPU-SW on board SW shall be capable to execute a CHECKOUT procedure (nominally a simulated descent) using CDMS DDBL information.

When commanded by the Probe CDMS the HASI-DPU-SW shall be capable to execute a set of special checkout functions.

PRE-SEPARATION phases shall comprise:

- GROUND C/O

- GROUND C/O SUSPENDED

- GROUND C/O DEACTIVATED

- FLIGHT C/O

PHASE

- FLIGHT C/O SUSPENDED

- FLIGHT C/O DEACTIVATED

After the Probe separation, some minutes (Tentry-5min) before the entry in the Titan atmosphere, HASI shall be powered on and the DDBL information received (the DDBL is broadcasted even before HASI is on). The HASI-DPU-SW then, shall recognize the Titan descent initiation and perform the predefined functions related to each POST-SEPARATION phase.

POST-SEPARATION phase shall comprise the TITAN DESCENT.

UR-3.1.1-1: The above mission phases shall be recognized by HASI-DPU-SW on the basis of the following DDBL information:

| TITAN DESCENT                                    | phase=0000                             | 0000 binary |

|--------------------------------------------------|----------------------------------------|-------------|

| GROUND SUSPENDED GROUND DEACTIVATED              | phase=0000<br>phase=0000<br>phase=0000 | 1100        |

| FLIGHT<br>FLIGHT SUSPENDED<br>FLIGHT DEACTIVATED | phase=1111<br>phase=1111<br>phase=1111 | 1100        |

DDBL INFO

UR-3.1.1-2 : GENERAL MISSION TIMELINE

Here follows a definition of mission sequence by events and time.

| EVENT TIME                                          | EVENT NAME                                       | EVENT DESCRIPTION                                                        |

|-----------------------------------------------------|--------------------------------------------------|--------------------------------------------------------------------------|

|                                                     | <del>                                     </del> | EVENT DESCRIPTION                                                        |

| -TBD years                                          | Launch                                           | Start CRUISE phase                                                       |

| -TBD years                                          |                                                  | FLIGHT checkouts                                                         |

| -TBD days                                           |                                                  | Pre-separation checkouts                                                 |

| -22 days                                            | Tsep                                             | Probe separation                                                         |

| 0:00                                                | Tp (-18 min to T0)                               | Probe activation                                                         |

| 8:00                                                | Thasi (-10 min to TO)<br>(Tentry-5min)           | Hasi activation<br>(STARTUP phase)                                       |

| +11:00                                              |                                                  | (start ENTRY phase)                                                      |

| +11:30                                              | Tacc                                             | Start sampling ACC                                                       |

| +13:00 min<br>(estimated)                           | Tentry                                           | Entry in the atmosphere                                                  |

| +18:00                                              | DDBL Time reset                                  |                                                                          |

| 0:00                                                | TO                                               | Mortar firing                                                            |

| + 0:01                                              |                                                  | Parachute deployment                                                     |

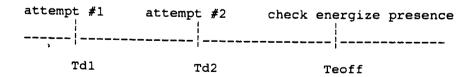

| + 0:55                                              |                                                  | Protected energize on                                                    |

| + 1:00                                              | Td1<br>Tdata                                     | (start DESCENT 1st phase)  1st Boom release try  Probe Relay Link activ. |

| + 1:55                                              |                                                  | 2nd HASI Power on                                                        |

| + 2:20                                              | Td2                                              | 2nd Boom release try                                                     |

| + 2:30                                              | TdataH                                           | (start DESCENT 2nd phase)                                                |

| + 3:25                                              | Teoff                                            | Protected energize off                                                   |

| + 10:00                                             | Tswitch                                          | Switch packet allocation                                                 |

| + 32 (*)                                            | Tradar                                           | (start DESCENT 3rd phase)                                                |

| + 133 min<br>(estimated based<br>on nominal profile |                                                  | Last Kilometer<br>(start IMPACT phase)                                   |

| +119 min                                            | Tproximity                                       | Start IMPACT phase when HASI is in BACKUP mode (i.e. DDBL absence)       |

| +135 min<br>(estimated)                             | Timpact                                          | Surface touch down<br>(start SURFACE phase)                              |

| +TBD min                                            | Tloss                                            | Loss of radio link<br>(END OF MISSION)                                   |

${\tt NOTE}\colon\thinspace {\tt Td2}$  must be greater than 2nd HASI power on time plus the time necessary to the startup function.

(\*) this time corresponds to  $T_A$  + 32 min ( $T_A$  is the arming time, that appens few seconds before T0).

### 3.1.2 HASI-DPU-SW OPERATIVE MODES

UR-3.1.2-1 : According to the mission events and phases and DDBL

information, the HASI-DPU-SW shall address the following

observable modes and states depicted here after :

| MODE                     | SUBMODE                          | STATE                                           |

|--------------------------|----------------------------------|-------------------------------------------------|

| STARTUP                  | n.a.                             | n.a.                                            |

| TITAN DESCENT            | NOMINAL/BACKUP                   | ENTRY/DESCENTI/DESCENT2/DESCENT3/IMPACT/SURFACE |

| CHECKOUT                 | NOMINAL/BACKUP ,                 | ENTRY/DESCENTI/DESCENT2/DESCENT3/IMPACT/SURFACE |

| TELECOMMAND<br>EXECUTION | NOMINAL/BACKUP                   | ENTRY/DESCENT1/DESCENT2/DESCENT3/IMPACT/SURFACE |

| UR-3.1.2-2 :             | The following ever mode:         | its shall cause the HASI-DPU-SW to change       |

|                          | - Power-on/reset                 |                                                 |

|                          | - Only at STARTU reception error | P the DDBL phases information or DDBL           |

|                          | - Executable Telec               | ommands                                         |

|                          | - Reset Telecomman               | d                                               |

The following events shall cause the  ${\tt HASI-DPU-SW}$  to change state inside an operational mode :

- Mission time evolution (TO, Tdata, TdataH, Tradar)

- Altimeter information

- Impact detection

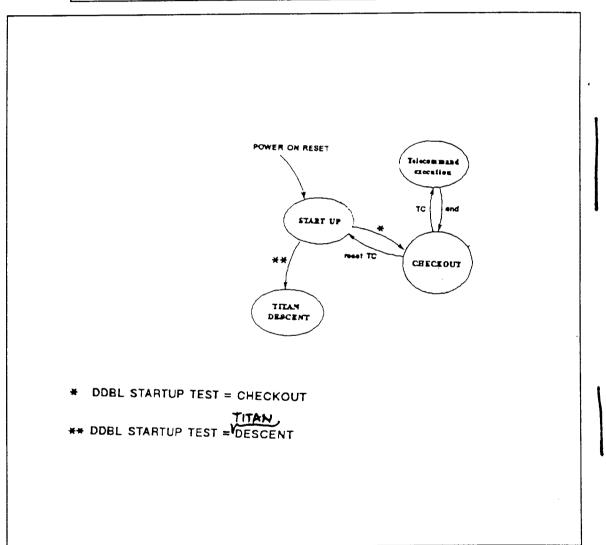

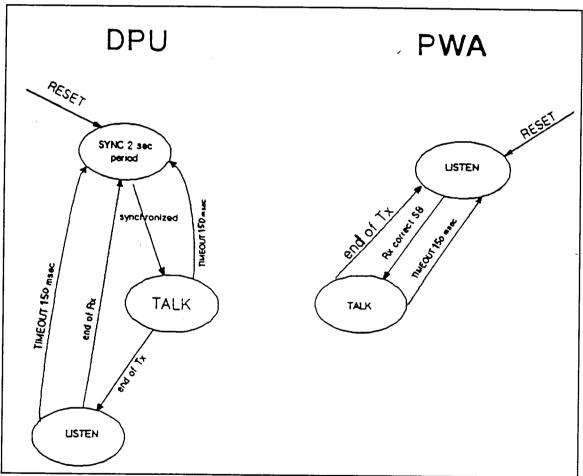

The mode changes are specified in the following table and in FIG 10.

The following events shall cause the HASI-DPU-SW to change submode inside an operational mode:

- DDBL reception errors

- BCP timeout (refers to 3.1.8-2)

The state changes are detailed inside each operative mode specification.

| \ dest.<br>source\       | STARTUP                           | TITAN<br>DESCENT                    | CHECKOUT                             | TELECOMMAND<br>EXECUTION   |

|--------------------------|-----------------------------------|-------------------------------------|--------------------------------------|----------------------------|

| STARTUP                  | - Power on<br>reset               | - STARTUP DDBL test = TITAN DESCENT | - STARTUP<br>DDBL test =<br>CHECKOUT | //                         |

| TITAN<br>DESCENT         | - Power on<br>reset               | //                                  | //                                   | //                         |

| CHECKOUT                 | - Power on<br>reset<br>- reset TC | //                                  | //                                   | -Executable<br>Telecommand |

| TELECOMMAND<br>EXECUTION | - Power on<br>reset<br>- reset TC | //                                  | - end of<br>telecommand<br>execution | //                         |

Figura 10 DPU OPERATIVE MODES

### UR-3.1.2-3 : STARTUP MODE ENTRY

As soon as the Power on reset or RESET telecommand is performed, the HASI-DPU-SW shall enter the STARTUP MODE and execute as specified in chapter 3.1.3.

#### UR-3.1.2-4: TITAN DESCENT MODE ENTRY

UR-3.1.2-4.1: After the STARTUP DDBL TEST of UR-3.1.3-2.1 results DESCENT mode the HASI-DPU-SW shall enter the TITAN DESCENT MODE and execute its mission program specified in chapter 3.1.4 driven by the DDBL information.

UR-3.1.2-4.2: In case of no correct reception of the DDBL, from both channels, within PAR1 (default PROM value = 3) minutes since power on reset HASI-DPU-SW shall consider to be in TITAN DESCENT MODE/BACKUP STATE and execute its mission program specified in chapter 3.1.4 driven by the internal MISSION time. (see STARTUP DDBL TEST UR-3.1.3-2.1)

UR-3.1.2.4-3: As soon as the TITAN DESCENT MODE is initiated, no other mode shall be taken in account by HASI-DPU-SW.

(i.e. only power off-on shall restart the HASI-DPU-SW).

### UR-3.1.2-5 : CHECKOUT (GROUND or FLIGHT) MODE ENTRY

After the STARTUP DDBL TEST of chapter 3.1.3 results CHECKOUT mode the HASI-DPU-SW shall start executing the CHECKOUT PROCEDURE as specified in chapter 3.1.5

UR-3.1.2-6 : DELETED.

# UR-3.1.2-7: TELECOMMANDS EXECUTION MODE (special checkout functions)

Telecommands use after the HASI AIV shall be foreseen only for contingency situation, while intensive use could be made during or before the AIV phase.

Telecommands shall be foreseen to be of two main classes according to their impact on the CHECKOUT PROCEDURES:

- EXECUTABLE TELECOMMANDS that conflict for mission resources and require a  ${\tt HASI-DPU-SW}$  operative mode change

- SETUP COMMANDS that do not require HASI-DPU-SW operative mode change

The detail of each Telecommand is specified in chapter 3.1.7.

### UR-3.1.2-7.1 : EXECUTABLE TELECOMMANDS

When the HASI DPU receives an EXECUTABLE TELECOMMAND, the present checkout procedure is suspended for the duration of the performing Telecommand.

The HASI internal status together with the results of the CHECKOUT FUNCTION are sent back by means of dedicated TM packets according to chapter 3.1.10.

At the end of the telecommand execution the HASI-DPU-SW shall restart the suspended checkout function and shall be ready to execute a new TC.

UR-3.1.2-7.2 : SETUP TELECOMMANDS

When HASI receives a SETUP TELECOMMAND, the pertained function is performed in a fraction of time (e.g. PWA test) without observable interruption of the running CHECKOUT procedure (i.e. NO HASI-DPU-SW MODE CHANGE)

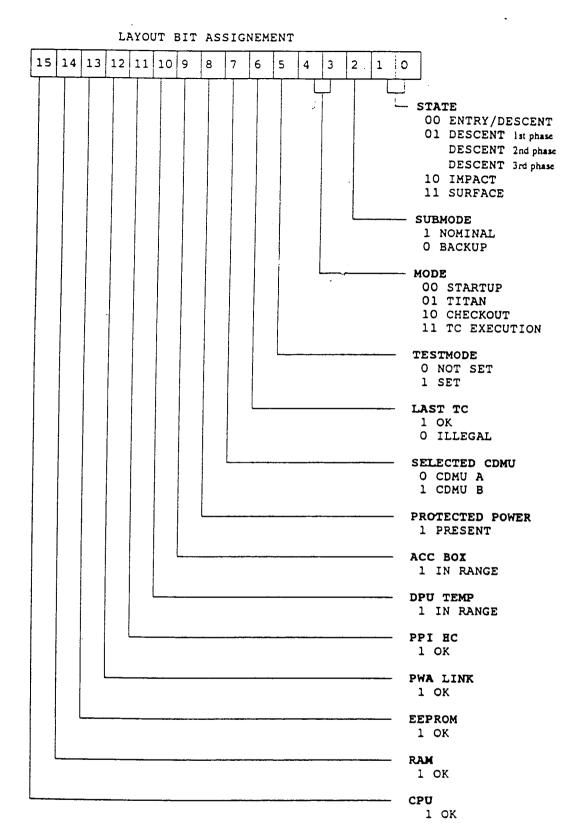

UR-3.1.2-8: The operative mode and status of the HASI-DPU-SW shall be uniquely identified by a bit pattern in the STATUS WORD (according to 3.2.2.1).

#### 3.1.3 STARTUP MODE

- - electronic devices WARM-UP of 300 msec is performed

- STATUS WORD bit #15 is set

- LOOK UP of possible reset cause (watch dog, reset TC, self reset due to program failure condition)

- load in RAM the PROM DEFAULT value of each UPLOADABLE item (tasks, functions and parameters)

- EEPROM test sequence

- clearing of all HW interfaces of chapter 3.2 (specially set MUX 2 on GND channel)

- set ACC range switch = FINE (Highest resolution)

- set STATUS WORD bit 14 to 1

- initialize internal HASI-DPU-SW MISSION TIME

#### UR-3.1.3-1.1 : EEPROM test sequence

UR-3.1.3-1.1.1 : EEPROM loocked:

- a- check the DDBL presence in both CDMU lines.

- b- check the received DDBLs

- c- in case of DDBLs corrupted (wrong CRC) or timeout (No DDBLs for a time greather than 14 sec), the HASI-DPU-SW shall load the EEPROM into RAM as per UR-3.1.3-1.1.2

- e- only in case of three DDBLs that show (FLIGHT/GROUND) CHECKOUT

with SPIN rate = 0xFF, the HASI-DPU-SW shall skip the activity of

UR-3.1.3-1.1.2.

This case will be reported by means of an EVENT and shall be sent

to ground via EVENT DATA packet.

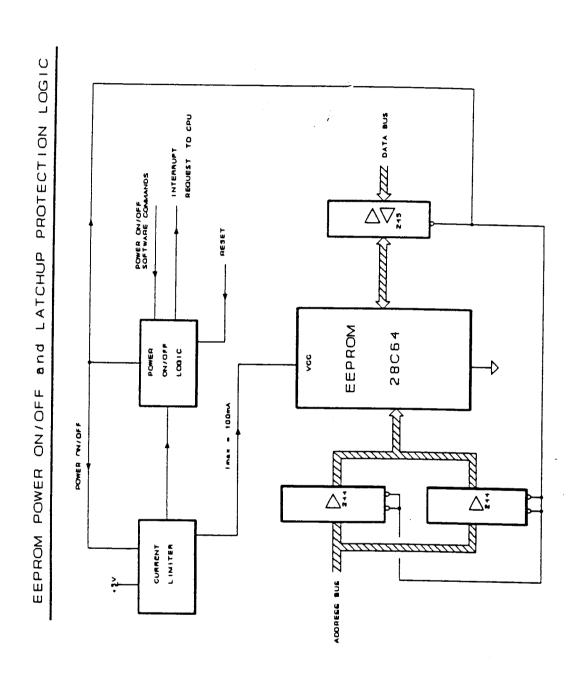

- ${\tt UR-3.1.3-1.1.2}$  : The <code>EEPROM</code> loading sequence shall be the following:

- a- EEPROM switch ON.

- b- search "EEPROM formatted" information (i.e. PARAMETER UPDATE BLOCK) and verify the CRC for each block.

- c- if the CRC is correct fill the RAM area with image contained in the EEPROM block.

- d- send a Startup Report (one for each EEPROM item) even if the CRC is computed.

- e- EEPROM switch OFF.

UR-3.1.3-1.1.2.1 : EEPROM formatted blocks shall be designed in order to allow the following SW maintenance operations:

- update/substitute of tables/parameters.

- correction/substitution of HASI-DPU-SW functions except the BOOM release.

UR-3.1.3-1.2 : DELETED

UR-3.1.3-2 : The following HEALTH CHECKS shall be performed

a- ADC1 3.2 Khz + DMA synchronization check

b- DDBL STARTUP TEST of correctness (UR-3.1.3-2.1)

Failures shall be reported by means of an EVENT and shall be sent to ground via EVENT DATA packet.

UR-3.1.3-2.1:

The DDBLs coming from both channels shall be examined starting with the channel as determinated by the PROCESSOR VALID signal to determine the HASI-DPU-SW operative mode to be entered according to the following table:

(DDBL channel A, DDBL channel B) --> HASI-DPU-SW MODE

| DDBL B                | ENTRY/DESCENT                         | CHECKOUT | RECEPTION             |  |

|-----------------------|---------------------------------------|----------|-----------------------|--|

|                       | flag                                  | flag     | NOK                   |  |

| ENTRY/DESCENT<br>flag | TITAN DESCENT TITAN DESCENT MODE MODE |          | TITAN DESCENT<br>MODE |  |

| CHECKOUT              | TITAN DESCENT                         | CHECKOUT | CHECKOUT              |  |

| flag                  | MODE                                  | MODE     | MODE                  |  |

| RECEPTION             | TITAN DESCENT                         | CHECKOUT | TITAN DESCENT         |  |

| NOK                   | MODE                                  | MODE     | MODE (*)              |  |

(\*) : see UR-3.1.2-4.2

UR-3.1.3-3 : DELETED

UR-3.1.3-4 : DELETED

UR-3.1.3-5 : The startup activities defined from UR-3.1.3-1 to 4 shall

be performed within 2 CDMS cycle, i.e. 32 sec.

UR-3.1.3-6: The Housekeeping activities of chapter 3.1.8 shall be

started as soon as possible.

#### 3.1.4 TITAN DESCENT MODE

#### UR-3.1.4-1 :

When in TITAN DESCENT MODE the following 6 states (mission phases) shall be recognized and operated by HASI-DPU-SW according to the evolving mission information :

- ENTRY: until Tdata

- DESCENT 1st PHASE: until TdataH

- DESCENT 2nd PHASE: until Tradar DESCENT 3rd PHASE: until Tproximity (in case BACKUP) until last kilometer (in case NOMINAL)

- IMPACT: Altitude < 1Km or after Tproximity

- SURFACE: after impact detected by ACC.

#### UR-3.1.4-2 :

There shall be two different way of driving the TITAN DESCENT thus leading to two different SUBMODES :

- NOMINAL MODE in which all the activities shall be driven by the DDBL information

- BACKUP MODE in which (because of incorrect DDBL or BCP) all activities shall be driven by DPU internal clock.

#### UR-3.1.4-3 : ENTRY PHASE

HASI will be powered on shortly (at Thasi) before the entry of the Probe into Titan atmosphere.

The HASI ENTRY phase starts after the Startup completion, just before the entry of the Probe into the Titan atmosphere and ends at the nominal instant of PRL activation (Tdata), 1 minute after the activation of the descent devices (mortar firing at TO instant). Its nominal duration is 11 minutes.

The HASI DPU SW shall execute its Entry phase mission programme:

- start ACC sampling after Tacc

- routing DDBL info to PWA and collect the PWA packets in accordance with requirements UR-3.1.14-2

- continuous acquire and buffer of time stamped ACC data according to chapter 3.1.11

- housekeeping functions as per chapter 3.1.8.

- create and enqueue time-stamped TM packets with data from above activities

- preliminary transmission of TM packets (according to CDMS polling rate) without discarding from the queue.

#### UR-3.1.4-4 :

DESCENT 1st PHASE

(before TdataH instant)

This subphase starts soon after the nominal PRL activation instant (Tdata instant) and ends 90 seconds after (TdataH instant = T0+2.5 min). Its nominal duration is 90 sec.

The HASI-DPU-SW shall execute its DESCENT 1st phase mission programme:

- sampling and time stamp of ACC, TEM, PPI science and HK data according to TM packet allocation scheme of 3.1.10

- perform 1st and the 2nd booms release attempt by means of MCA activation bursts according to chapter 3.1.15

- housekeeping functions as per chapter 3.1.8

- routing DDBL info to PWA and collect the PWA packets in accordance with requirements UR-3.1.14-2

- create and enqueue time-stamped TM packets with data from above activities

- preliminary transmission of TM packets (according to CDMS polling rate) without discarding from the queue.

####

This subphase starts soon after the TdataH instant and ends at (Tradar instant). Its nominal duration is 29.5 minutes.

The HASI-DPU-SW shall execute its DESCENT 2nd phase mission programme:

- sampling and time stamp of ACC, TEM, PPI science and HK data

- routing DDBL info to PWA and collect the PWA packets in accordance with requirements UR-3.1.14-2

- housekeeping functions as per chapter 3.1.8

- create and queue time stamped TM packets with data from above activities and from PWA data packets

- restart transmission of TM packets (acquired during ENTRY and DESCENT 1st phase) according to CDMS polling rate with queuediscarding.

####

This subphase starts soon after the **Tradar instant** and ends at the recognition of the proximity of the impact. Its nominal duration is 101 minutes.

The HASI-DPU-SW shall execute its DESCENT 3rd phase mission programme:

- sampling and time stamp of ACC, TEM, PPI science and HK data

- routing DDBL info to PWA and collect the PWA packets in accordance with requirements UR-3.1.14-2

- housekeeping functions as per chapter 3.1.8

- create and queue time stamped TM packets with data from above activities and from PWA data packets

- transmission of TM packets according to CDMS polling rate

- synchronization with CDMS and recognition of Proximity of impact

UR-3.1.4-6.1: The determination of Proximity of the impact shall be performed as follows:

if the DDBL is OK the proximity of impact shall occur when the

measured or predidected altitude (in DDBL) indicates the last Km

otherwise

if the DDBL is absent the proximity of impact shall occur when 119 minutes are elapsed since TO. (i.e. the shortest mission profile is considered the worst case)

### UR-3.1.4-7 : IMPACT PHASE

This subphase starts at the recognition of the proximity of the impact, ends at the recognition of the impact (Timpact instant) by analysis of ACC data. Its nominal duration is 2 minutes.

The HASI-DPU-SW shall execute its IMPACT phase mission programme:

- sampling and time stamp of ACC, TEM, PPI science and HK data

- routing DDBL info to PWA and collect the PWA packets in accordance with requirements UR-3.1.14-2

- housekeeping functions as per chapter 3.1.8

- create time stamped TM packets with data from above activities

- determine Timpact instant by processing on-line of ACC Xservo data

- create time stamped TM packets of ACC impact frames as detailed in chapter 3.1.11

- transmission of TM packets according to CDMS polling rate

- N.E. UR-3.1.4-7.1: The ACC requirements at IMPACT (i.e. UR-3.1.11-9) shall reside in EEPROM area and shall be loaded in RAM at START-UP; the default PROM value for the ACC requirements at IMPACT shall performe the ACC activities as in DESCENT 3rd phase (i.e. UR-3.1.11-8) (NOT ESSENTIAL)

### UR-3.1.4-8 : SURFACE PHASE

This subphase starts soon after the recognition of the impact event (Timpact instant) and never ends but keep on until battery power is exhausted or telemetry link is loss (Tloss instant). Its nominal duration is 30 minutes max.

During this phase the software shall perform the same activities of UR-3.1.4-6 (DESCENT 3rd PHASE) execpt for UR-3.1.4-6.1.

NOTE: HASI SURVIVAL AFTER IMPACT IS NOT CERTAIN.

### 3.1.5 CHECKOUT MODE

UR-3.1.5-1: After the DDBL STARTUP TEST results checkout the HASI-DPU-

SW shall start executing the predefined CHECKOUT PROCEDURE (i.e. the simulated descent) identical to the TITAN DESCENT MODE functions except the MCA activation of chapter 3.1.15

shall never be performed.

UR-3.1.5-2: DELETED

UR-3.1.5-3 : DELETED

UR-3.1.5-4 : DELETED

UR-3.1.5-5: During the CHECKOUT MODE HASI-DPU-SW shall be able to

accept and execute Telecommands as defined in chapter 3.1.7; after the execution the interrupted CHECKOUT

PROCEDURE shall be restarted.

### 3.1.6 SHUTDOWN MODE: DELETED

### 3.1.7 TELECOMMANDS MANAGEMENT

- UR-3.1.7-1 During the CHECKOUT phases the HASI-DPU-SW shall be able to execute, if correctly received, telecommands outlined here after:

- SOFT RESET

- PWA TEST

- TEST MODE

- DUMP MEMORY

- LOAD HASI MEMORY

- UR-3.1.7-2 Each Telecommand shall comply to ESA-PSS-04-107 Telecommand Packet Standard.

The general Telecommands protocol is defined in EID part A document sect. 3.6.3.6-1, while detail of each Telecommand layout is defined in HASI-IDS.

UR-3.1.7-3 Each Telecommand received during a different mission phase from CHECKOUT shall be ignored.

The dedicated error bit # 6 of the STATUS WORD shall be updated according to chapter 3.2.2.1 and left unchanged until the next telecommand is received or the DPU is reset.

UR-3.1.7-4 Each Telecommand incorrectly received (i.e. not in compliance with specifications of UR-3.1.7-2) shall be ignored and the event shall be recorded in the MISSION HISTORY LOG FILE.

The dedicated error bit # 6 of the STATUS WORD shall be updated according to chapter 3.2.2.1 and left unchanged until the next telecommand is received or the DPU is reset.

UR-3.1.7-5 Telecommands sent before the completion of another Telecommand shall be ignored.

The dedicated error bit # 6 of the STATUS WORD shall be updated according to chapter 3.2.2.1 and left unchanged until the next telecommand is received or the DPU is reset.

### UR-3.1.7-6 As soon as a telecommand is successfully received:

- the error bit # 6 of the STATUS WORD shall be updated according to chapter 3.2.2.1;

- a TC echo TM packet shall be sent to both channel with highest priority;

- the pertaining functions shall be performed as detailed hereafter according to the command header (function number).

#### UR-3.1.7-6.1 SOFT RESET

- wait at least 18 sec after its reception

- restart the program from bootstrap leaving the watch\_dog to reset the DPU.

#### UR-3.1.7-6.2 PWA TEST COMMAND

The PWA Test Command Number received is inserted in the dedicated "socket" (PWA TEST PARAM) of the next STATUS BLOCK to be transmitted to PWA.

SIMULATED DESCENT shall not be affected.

### UR-3.1.7-6.3 TEST MODE

This command shall be used to health check the Memory Load lines TM lines and Status Word:

the HASI-DPU-SW shall be set/reset the STATUS WORD bit # 5 according to the command argument.

### UR-3.1.7-6.4 DUMP MEMORY

- The requested consecutive memory location are dumped according to chapter 3.2.5.2 into dedicated TM packets taken from science allocated ones (PWA science).

- The checkout mode (nominally SIMULATED DESCENT) shall not be interrupted until the command is finished. Then the SIMULATED DESCENT shall restart.

### UR-3.1.7-6.5 LOAD HASI MEMORY

- The requested EEPROM, RAM locations (physical addresses) are loaded according to chapter 3.2.5.1

- Report of verified loaded locations is reported by means of 1 dedicated TM packet taken from science allocated ones (PWA science).

- The checkout mode (nominally SIMULATED DESCENT) shall not be interrupted.

|        | _   |       |         |

|--------|-----|-------|---------|

| UR - 3 | .1. | 7-6.6 | DELETED |

UR-3.1.7-6.7 DELETED

UR-3.1.7-6.8 DELETED

UR-3.1.7-6.9 For each unknown command an event shall be recorded in the MISSION HISTORY LOG FILE.

### 3.1.8 HOUSEKEEPING (Periodical functions)

- UR-3.1.8-1: At a multiple of DDBL rate (nominally each 16 sec.) HASI-DPU-SW shall perform the following periodical functions (the HK TM bit allocation is reported in brackets):

- a- measure of DPU box internal temperature (16 bit)

- b- health check of the DPU housekeeping voltages (1 bit)

- c- updating of the following bit of the STATUS WORD

PWA link status

PPI frequency status

DPU internal temp

ACC internal temp

HASI-DPU-SW status

Protected Power presence

- UR-3.1.8-2 : At DDBL rate (nominally each 2 sec.) HASI-DPU-SW shall

perform the following periodical functions :

- a- health check of BCP pulse rate (1 bit)

- b- health check of PPI HC voltages range (2 bit)

- c- health check of incoming DDBL (1 bit)

- $\mbox{d-}$  if last DDBL is not okay or BCP is not okay or VALID line has been swapped by CDMS then swap selected CDMU

- e- if last DDBL was not okay shift DDBL rate HK activities (e.g. 1 BCP time duration) in order to ensure avoiding of self disturbing the ML and BCP line by CDMU swapping

- f- if last BCP was not okay shift DDBL rate HK activities (e.g. 1/2 BCP time duration) in order to ensure avoiding of self disturbing the ML and BCP line by CDMU swapping

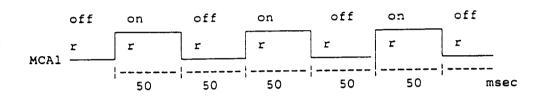

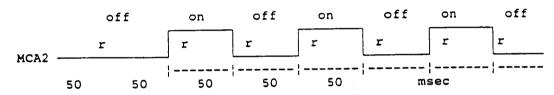

- g- readout of MCA interface: Protected Power Presence, MCAl status and MCA2 status (3 bit)

- h- health check of PWA data link (1 bit)

- i- health check of PPI frequency output line (1 bit)

- j- ADC-2 correct working (1 bit)

- k- XSERVO Range selection (1 bit)

- 1- PWA status: Science or Test (1 bit)

- see also UR-3.1.9-2

- UR-3.1.8-3 DELETED

- UR-3.1.8-4 16 bit (1 word) shall be allocated for each 2 second HC report and

collected in a dedicated TM packet.

- UR-3.1.8-5 56 bit (7 bytes) shall be allocated for history log of not

periodical event. Each event shall have a unique code number, 24

bit mission time, 8 bit Time Flag and an event data field and

shall be collected in dedicated type of HK TM packet.

- UR-3.1.8-5.1 Maximum 64 events for each event code number shall be

possible.

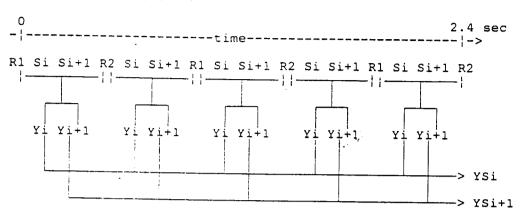

#### DESCENT DATA BROADCAST LIST 3.1.9

The HASI functions and mission time shall be always UR-3.1.9-1 : determined by the DDBL provided every 2 seconds by the CDMS through the ML I/F except :

Since the DPU HW allow reception of only one ML UR-3.1.9-1.1 : channel at a time, in case of incorrect reception of DDBL packets (because of the following rejection criteria) the HASI-DPU-SW shall base its functions upon the internal clock and shall record the event in the HK history LOG event FILE that shall be telemetred to Ground.

DDBL rejection criteria: UR-3.1.9-1.2 :

- 1) Reception timeout of 1 BCP duration.

- 2) Invalid Packet Format or invalid CRC.

NOTE: see UR-3.1.8-2

The DDBL layout (standard ESA TC packet) is defined in EID UR-3.1.9-2 : part A sect. 3.6 . Its content are :

- Time elapsed in two segments separated by a 1) reset at TO:

- from CMDS turn-on to TO

- from TO to the end of mission

- Altitude of the Probe 2)

- Spin rate of the Probe 3)

- Mission phases : 4)

- Entry-Descent

Ground checkout /active/suspended/deactivated Flight checkout /active/suspended/deactivated

When the MISSION PHASE flags show the pattern for GROUND UR-3.1.9-3 : CHECKOUT (0000 0011) or FLIGHT CHECKOUT (1111 0011), the HASI-DPU-SW shall initiate the SIMULATED DESCENT, described in chapter 3.1.12, according to the MISSION TIME contained in the DDBL.

NOTE: during CHECKOUT modes DDBL parameters can take any value in order to allow to skip different time part of the mission to be simulated.

- When the MISSION PHASE flags show the pattern for GROUND UR-3.1.9-4 : CHECKOUT SUSPENDED (0000 1100) or FLIGHT CHECKOUT SUSPENDED (1111 1100), the HASI-DPU-SW shall continue the SIMULATED DESCENT (with frozen time) until a TELECOMMAND or a new MISSION PHASE flag set.

- When the MISSION PHASE flags show the pattern for GROUND UR-3.1.9-5 : CHECKOUT DEACTIVATE (0000 1111) or FLIGHT CHECKOUT DEACTIVATE (1111), the HASI-DPU-SW close and Tx all the HK EVENT LOG packets.

# DDBL MISSION PHASES DEFINITION

MISSION PHASE

PATTERN (binary)

| 0000 0000 |

|-----------|

| 0000 0011 |

| 0000 1100 |

| 0000 1111 |

| 1111 0011 |

| 1111 1100 |

| 1111 1111 |

|           |

#### 3.1.10 TELEMETRY DATA MANAGEMENT

UR-3.1.10-1 : The HASI-DPU-SW shall communicate data to ground by means of Telemetry packet through the CMDS I/F depicted in chapter 3.2.2.2.

UR-3.1.10-2 : The used Telemetry packets shall comply to ESA-PSS-04-106 Telemetry Packet Standard. The general protocol is defined in EID part A document section 3.6.3.7, while details of TM packets lay-out are defined in the HASI IDS.

UR-3.1.10-3 : There shall be up to 255 possible different TM data packets format: one for each data item to be transmitted as defined in HASI-IDS table "TELEMETRY PACKET DATA FORMAT".

UR-3.1.10-3.1 : Each data item to be transmitted has associated a predefined production rate and a bit allocation for produced item (resolution = 1 byte = 8 bits).

NOTE: The largest multiple of the bit allocation that fits in the 112 byte data field of the TM packet determines the utilization percentage of each TM packet.

UR-3.1.10-3.2 : The sum of all data item of the same source (DPU, ACC, TEM, PPI, PWA) must comply with the CDMS packet/cycle "HASI DATA RATE BUDGET" table shown hereafter.

NOTE: THE ALLOCATED RATE MUST BE CONVERTED IN A EQUIVALENT INTEGER NUMBER OF PACKET RATIO (e.g. 0.1 packet/cycle = 1 packet/160 seconds)

UR-3.1.10-3.3 : The data items contained in each TM packet shall be ordered in production chronological order and nominally result from periodical processing of periodical sampled raw data.

UR-3.1.10-3.4: Each TM packet shall be time stamped with the processing instant of the first data item contained in the packet. The accuracy of time is better than 125 msec (worst case). Special TM packets like HOUSEKEEPING or STARTUP reports shall use event occurring or data creation time.

UR-3.1.10-4 : The TM packets shall be enqueued for transmission to CDMS according to their source with the following priorities (decreasing order) :

GROUP 1 : TC REPORTS / HK / ACC ENTRY / ACC IMPACT TEM / PPI / ACC / PWA

GROUP 2 :

All the TM packets shall be a single copy to be transmitted on both channel A and B except for PWA packets that it shall be different for both the two UR-3.1.10-4.1 :

Telemetry transmission to CDMUs shall always be performed UR-3.1.10-5 : as follow:

- 1. until TdataH Transmission is redundant

- 2. after TdataH Transmission is nominal

- in case of TC reception (while in CHECKOUT opmode of the HASI-DPU-SW) Tranmission shall be nominal until DPU reset.

UR-3.1.10-6 : DELETED

CASSINI HASI data rate budget - minimum allocation pitraenew.wk1 Apr. 1995 - Proximity sensor ON at Ta+32' => Tradar= T0+32' T0+32' T0+85' T0+133' T0+135' T0+165' T0+1' T0+10' T0+2.5' T0-10' T0-6' Timeline Tdata Tdatah Tradar Tprox Timp Tloss Tacc Thasi 60.0 18.0 1,0 0,0 130,0 1270,0 160.0 Altitude +133 +85 +135 +10 +32 +165 +1 +2.5 -6 -10 ime [min] 22,00 53,0 48,00 2.00 30.00 7,50 7,00 1,50 4,00 duration [min] 8 199 181 113 6 29 83 27 worst-case cycles 16 0,75 0,75 0.00 1,00 1.50 0.00 0.00 1.50 1,50 ACC [pack/cycle] 3.00 1.50 1,50 0.00 2,00 3,00 3,00 0.00 0,00 A&B [pack/cycles] 0,0 226,0 298,5 271,5 249,0 0,0 18,0 87.0 On A&B [packets] 0,0 0,0 0,0 0.0 66.0 86,0 0,0 0,0 0,0 0,0 extra packets 298,5 271,5 0,0 358,0 87,0 249,0 18,0 0,0 172,0 total packets 0.50 0.50 0,50 0.50 0.50 0.50 0.50 0.00 0,00 PRE [pack/cycle] 1,0 1,0 1,0 1,0 0.0 1.0 1,0 1,0 0,0 Ch A&B [pack/cycles] 199,0 181,0 8,0 113,0 29,0 83,0 6,0 0,0 0,0 Ch\_A&B [packets] 0,50 0,50 0.50 0.50 0.50 0.50 0,50 0.00 0.00 TEM [pack/cycle] 1,0 1,0 1,0 1,0 1,0 0.0 1,0 1,0 0,0 Ch A&B [pack/cycles] 181,0 8,0 113,0 199,0 29,0 83,0 0.0 6,0 0,0 Ch A&B [packets] 12,00 14,00 12,00 11,50 11,50 0.00 0,00 0,00 12,00 PWA [pack/cycle] 2,00 0,00 0,00 2,00 2,00 0,00 0,00 0.00 0.00 RAE [pack/cycle] 13,5 13,5 16,0 12.0 0,0 12.0 12,0 0,0 0.0 Ch A&B [pack/cycles] 128,0 1356,0 2686,5 2443,5 0,0 348,0 996.0 0,0 CH\_A&B [packets] 0,0 0,20 0,20 0,20 0.20 0,20 0,20 0,20 0,20 0,20 Hskp [pack/cyc] 0.40 0.40 0,40 0.40 0.40 0,40 0,40 0,40 0,40 Ch\_A&B [pack/cycles] 79,6 72,4 3,2 45,2 33,2 2,4 11,6 10,8 6.4 Ch. A&B [packets] 0,0 0,0 0,0 0.0 0,0 0,0 3,0 3.0 3,0 extra packets 72 3 45 33 80 12 17 8 12 total packets 15,45 17,20 14,20 15,45 0,20 2,70 14,70 14,70 0,20 science req. (1) 17,40 17,40 18,40 16,40 17,40 17,40 5,40 0.40 0,40 Ch A&B req. (1) 3149 147 1985 3463 189 38 505 1444 12 total req.[pack] 744 2188 5651 5338 5485 7323 240 12 201 progr.req.[pack] Alloc.[pack/cyc] 9 9 9 9 9 0 14 0 0 Channel A 9 9 9 9 9 0 0 14 0 Channel B 3582 3258 144 2034 1494 0 812 0 0 Alloc. [pack] 5564 5708 7742 5888 0 0 812 2306 0 progr.all.[pack] -3 49 307 50 119 109 -189 -38 -12 delta pack [r-a] -3 46

prog. delta pack

-12

-201

50

68

-240

109

119

## 3.1.11 ACC FUNCTIONAL REQUIREMENTS

UR-3.1.11-1 : The following ACC RAW DATA (from RD1 to RD7) shall be the

base for the subsequent depicted processing. They shall be

selected picking 1 each n from each ADC channel (sampled at

nominally 400Hz, see ACC I/F) to obtain the following rates

at least:

RD1. Xservo LOW GAIN 12bit @100Hz

RD2. Xservo HIGH GAIN 12bit @100Hz (n=4)

RD3. Xpiezo 12bit @50Hz (n=8)

**RD4.** Ypiezo 12bit @50Hz (n=8)

**RD5.** Zpiezo 12bit @50Hz (n=8)

**RD6.** Temp1 12bit @1.5625Hz (n=256)

RD7. Temp2 12bit @1.5625Hz

UR-3.1.11-2 : The following SCIENCE DATA shall be produced by means of block integration (sum of n consecutive samples) of N RAW DATA :

SCDSE. best Xservo channel 16 bit @3.125 Hz N=32 channel selection flag 1 bit @3.125 Hz

Total 17 bit @3.125 Hz

SCDSD. best Xservo channel 16 bit @4.167 Hz N=24 channel selection flag 1 bit @4.167 Hz

Total 17 bit @4.167 Hz

SCDSR. best Xservo channel 16 bit @1.754Hz N=57 channel selection flag 1 bit @1.754Hz

Total 17 bit @1.754Hz

SCDPX. Xpiezo value 16 bit @1.6129Hz N=31

SCDPY. Ypiezo value 16 bit @1.6129Hz N=31

SCDPZ. Zpiezo value 16 bit @1.6129Hz N=31

UR-3.1.11-3 : The following HOUSEKEEPING DATA shall be produced by means of block integration (sum of n consecutive samples) of N RAW DATA :

**HKD1.** Sum of RD6 (Temp1) 16 bit @0.097 Hz N=16

**HKD2.** Sum of RD7 (Temp2) 16 bit @0.097 Hz N=16

HKD2 shall be started half period (about 5 seconds) after HKD1.

UR-3.1.11-4: The following STATISTIC DATA shall be produced from a different selection of 1 each n from each ADC channel according to the following scheme:

STD2. Is Sum of 128 samples picked 1 every 32 (i.e. 42 @12.5 Hz)

Xs : 24 bit (\*) @0.1Hz Xp : 24 bit (\*\*) @0.1Hz Yp : 24 bit (\*\*) @0.1Hz Zp : 24 bit (\*\*) @0.1Hz

(\*) 24 = 22 sum + 1 best + 1 spare

(\*\*) 24 = 22 sum + 2 spare

UR-3.1.11-5 : DELETED

UR-3.1.11-6 : The following activities shall be performed since the Tacc=11.30 min DDBL time (during ENTRY phase) up to the Tdata instant for a maximum of 7.30 min = 450 sec :

- Perform UR-3.1.11-1 + UR-3.1.11-2 + UR-3.1.11-3 + UR-3.1.11-4 a -

- Create less than 100 TM packets (of 112 data field each corresponding to a total of 11200 bytes) according to the hfollowing scheme :

- 1. SCDSE :  $450 \sec x \ 3.125 Hz = 1407 \ samples$ = 28 TMpack

- 2. SCDPX:  $450 \sec x 1.6129 Hz = 726 samples$ = 13 TMpack(\*)

- 3. SCDPY: same as above = 13 TMpack(\*)

- SCDPZ : same as above = 13 TMpack(\*)

- STD2.Xs :  $450 \sec x \ 0.1 Hz = 45 \ samples$ 5. = 2 TMpack(\*\*)

- STD2.Xp : 6. same as above = 2 TMpack(\*\*)

- 7. STD2.Yp : same as above = 2 TMpack(\*\*)

- STD2.Zp : same as above = 2 TMpack(\*\*)

- 9. HKD1 :  $450 \sec x \ 0.1 Hz = 45 \ samples$ = 1 TMpack

- 10. HKD2 : 450 sec x 0.1 Hz = 45 samples= 1 TMpack

\_\_\_\_\_\_ Total data production = 77 Tm packets

- Enqueue the above 77 TM packets for redundant transmission to C-CDMS.

- each piezo packet has 52 samples

- (\*\*) each STD2 has 37 samples

- The following shall be performed during DESCENT 1st phase UR-3.1.11-7.1 : up to the DESCENT 2nd phase: since Tdata instant till TdataH instant (nominally from T0+1 to T0+2.5 for total 1.5min = 90sec):

- Perform UR-3.1.11-1 + UR-3.1.11-2 + UR-3.1.11-3 + UR-3.1.11-4 a-

- Create TM packets of ACC data (at the rate of 1.5/CDMS cycle bcorresponding to 10.5 byte/sec = 84 bit/sec) composed of the following items :

- 1. SCDSD : 17bit x 4.167Hz = 70.84 bit/sec

- 2. STD2 : 96bit x 0.1Hz = 9.6 bit/sec

- 3. HKD1 : 16bit x 0.1Hz = 1.6 bit/sec

- 4. HKD2: 16bit x 0.1Hz = 1.6 bit/sec

Total data produced = 83.64 bit/sec Total produced packets = 8

Enqueue the above packets for redundant transmission to CDMS

- UR-3.1.11-7.2 : The following shall be performed during DESCENT 2nd phase

up to the DESCENT 3rd phase: since TdataH instant till

Tradar instant (nominally from T0+2.5 to T0+32 for total

29.5min = 1770sec) :

- a- Perform UR-3.1.11-1 + UR-3.1.11-2 + UR-3.1.11-3 + UR-3.1.11-4

- b- Create TM packets of ACC data (at the rate of 1.5/CDMS cycle corresponding to 10.5 byte/sec = 84 bit/sec) composed of the following items:

- 1. SCDSD : 17bit x 4.167Hz = 70.84 bit/sec

- 2. STD2 : 96bit x 0.1Hz = 9.6 bit/sec

- 3. HKD1 :  $16bit \times 0.1Hz$  = 1.6 bit/sec

- 4. HKD2: 16bit x 0.1Hz = 1.6 bit/sec

------

Total data produced = 83.64 bit/sec

- c- Enqueue the above packets for transmission to CDMS

- - a- Perform UR-3.1.11-1 + UR-3.1.11-2 + UR-3.1.11-3 + UR-3.1.11-4

- b- Create TM packets of ACC data (at the rate of 0.75/CDMS cycle corresponding to 5.25 byte/sec = 42 bit/sec) composed of the following items:

- 1. SCDSR : 17bit x 1.754Hz = 29.82 bit/sec

- 2. STD2 : 96bit x 0.1Hz = 9.6 bit/sec

- 3. HKD1: 16bit x 0.1Hz = 1.6 bit/sec

- 4. HKD2 : 16bit x 0.1Hz = 1.6 bit/sec

Total data produced = 42.62 bit/sec

c- Enqueue the above packets for transmission to CDMS

- - a- Perform UR-3.1.11-1

- b- Store the 6 sec trace of the impact [Timpact-0.5sec, Timpact+5.5sec] containing the following IMPACT TRACE DATA selected picking 1 each n from each ADC channel (sampled at nominally 400Hz, see ACC I/F) obtaining the following rates:

- ID1. Xpiezo 16bit @200Hz n = 2 200Hz x 6sec = 1200 samples = 22 TM

- **ID2.** Ypiezo 16bit @200Hz n = 2 200Hz x 6sec = 1200 samples = 22 TM

- ID4. Xservo LOW GAIN 12bit @400Hz n = 1

- c- Determine the Timpact instant basing upon XPn filtered threshold

crossing with the following quadratic filter:

XPn = A\*XPn-2 + B\*XPn-1 + C\*XP

where XP represents the 400 Hz Xservo LOW GAIN acceleration signal (ID4) and XPn filtered Xservo values.

c.1- The A, D, C, Th shall be uploadable parameters; they shall have the following ranges:

> A = -1 to 1 B = -1 to 1 C = -1 to 1Th > 0

The PROM default values shall be:

A = 0.1 B = 0.2 C = 0.7 Th = 5 Volt

- - a- Create a set of **66 TM packets** containing the impact trace from the above stored IMPACT TRACE DATA.

- b- Enqueue the above packets for transmission to CDMS with the following priority-layout : ID1+ID2+ID3

- c- Perform UR-3.1.11-1 + UR-3.1.11-2 + UR-3.1.11-3 + UR-3.1.11.4

- e- Create TM packets of ACC data (at the rate of 1/CDMS cycle corresponding to 7 byte/sec = 56 bit/sec) composed of the following items:

- 1. SCDSR : 17bit x 1.754Hz = 29.82 bit/sec

- 2. STD2 :  $96bit \times 0.1Hz = 9.6 bit/sec$

- 3. HKD1 :  $16bit \times 0.1Hz = 1.6 bit/sec$

- 4. HKD2 : 16bit x 0.1Hz = 1.6 bit/sec

Total data produced = 42.62 bit/sec

- c- Enqueue the above packets for transmission to CDMS

- UR-3.1.11-11 : XSERVO RANGE SELECTION :

- ${\tt UR-3.1.11-11.1}: {\tt After POWER-ON} \ {\tt or RESET} \ {\tt the range switch shall be set to FINE}.$

IF "PARthresholdRANGE (default PROM value =95%) trepassed "THEN set range switch to COARSE

The number of samples examined for the above purpose shall be determined in order to not overload the CPU with this low rate task for no more of 1/1000 of CPU load.

UR-3.1.11-12 : BEST XSERVO CHANNEL SELECTION :

UR-3.1.11-12.1: After POWER-ON or RESET the selected Xservo channel shall be LOW (RD2).

UR-3.1.11-12.2: Raw data item RD1 and RD2 shall be periodically examined once each block N for each SCDSE, SCDSD and SCDSR in order to select in the following way best Xservo channel to be used:

case Xservo = LOW GAIN

if ABS(Xservo) < "PARXservoLow (default PROM value

=7%)"</pre>

select Xservo = HIGH GAIN

case Xservo = HIGH GAIN

if ABS(Xservo) > "PARXservoHigh (default PROM value =90%)"

select Xservo = LOW GAIN

The number of samples examined for the above purpose shall be determined in order to not overload the CPU with this low rate task for no more of 1/1000 of CPU load.

UR-3.1.11-13: The actuation of XSERVO range and the selection of XSERVO best channel shall be synchronized with the start of SCDS\* blocks.

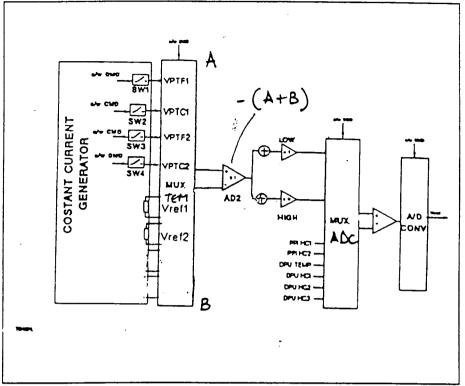

### 3.1.12 TEM MANAGEMENT

### TEM sensor layout

HEAD 1 ( TEM 1 )

(V) PTF1 (voltage) thermistor fine sensor 1

(V) PTC1 (voltage) thermistor coarse sensor 1

HEAD 2 ( TEM 2 )

(V) PTF2 (voltage) thermistor fine sensor 2

(V) PTC2 (voltage) thermistor coarse sensor 2

#### COMMON TO BOTH HEADS

(V) REFLOW (voltage) reference for low gain

(V) REFHIGH (voltage) reference for high gain

4 CURRENT GENERATOR: 1 for each sensor

2 GAIN: 1 for each measure

(see I/F layout 3.2.3.6.2 chapter)

- UR-3.1.12-1: The following SCIENCE DATA <u>measurement set</u> shall be performed cyclically every 5 seconds in the same way during all the states of the TITAN DESCENT or CHECKOUT modes after Tdata instant (i.e. states DESCENT 1st PHASE, DESCENT 2nd PHASE, DESCENT 3rd PHASE, SURFACE):

- 0 sec measurement set of F1 (Fine Sensor #1)

- 1.25 sec measurement set of C1 (Coarse Sensor #1)

- 2.5 sec measurement set of F2 (Fine Sensor #2)

- 3.75 sec measurement set of C2 (Coarse Sensor #2)

the measurement set is defined in UR-3.1.12-2.

- UR-3.1.12-1.1: The following SCIENCE DATA <a href="mailto:measurement\_set">measurement\_set</a> shall be performed cyclically every 6 seconds in the following way during the IMPACT state of the TITAN DESCENT or CHECKOUT modes:

- 0 sec measurement set of F1 (Fine Sensor #1)

- 1.25 sec measurement set of F2 (Fine Sensor #2)

- 2.5 sec measurement set of F1 (Fine Sensor #1)

- 3.75 sec measurement set of F2 (Fine Sensor #2)

the measurement set is defined in UR-3.1.12-2.

### UR-3.1.12-2 : <u>Measurement set definition</u>

For each sensor x = F1, C1, F2, C2 a voltage measurement set combined with gain selection and current generator switching on off shall be performed in the following sequence within 130 msec max:

- O2DVTx = averaged offset (1) of (2(VPTx VREFy)) obtained according to 3.2.3.8.2.2

- O2VRy = averaged offset (1) of (VREFy + VREFy) obtained according to 3.2.3.8.2.2

- D2VTx = averaged value (2) of (2(VPTx VREFy)) obtained according to 3.2.3.8.2.1

- 2VRy = averaged value (2) of (VREFy + VREFy) obtained according to 3.2.3.8.2.1

- y = LOW/HIGH gain selection on MUX AD according to threshold crossing criteria of 3.1.12.3

- (1) i.e. current generators off

- (2) i.e. current generators on

# UR-3.1.12-3 : Measurement\_set (bit allocation) layout

Each sensor measurement set shall be composed of two 24 bits groups to easy TM packeting functions.

O2DVTx LSB = 7 bit sensor offset voltage (\*)

D2VTx = 16 bit sensor voltage (\*\*)

selected gain = 1 bit gain selection flag (0 = L / 1 = H)

Total GROUP T = 24 bit

O2VRx LSB = 7 bit reference offset voltage (\*)

2VRx = 16 bit reference voltage (\*\*)

selected gain = 1 bit gain selection flag (0 = L / 1 = H)

Total GROUP R = 24 bit

GROUP T = Thermistor data

GROUP R = Reference voltage data

- (\*) (resolution = 1 ADU/4)

- (\*\*) (resolution = 1 ADU/8)

Each measurement\_set shall be contained in a single packet.

UR-3.1.12-3.1 : For each sensor measurement, the HASI-DPU-SW shall

produce:

OVFMEAN = 16 bit offset thermistor voltage (resolution 1/8 ADU)

OVRMEAN = 16 bit offset reference voltage (resolution 1/8 ADU)

The two offsets shall be the average (running mean @108 sec) of thermistor (reference) voltage offset i.e. O2DVTx (O2VRy).

### UR-3.1.12-4 : Gain selection criteria

For each sensor x the low or high gain channel y is selected at the end of the measurement set using the following algorithm with the preceding measurement set values and the preceding gain selection:

${\tt UR-3.1.12-4.1}$ : The rough resistors Ratio RRx (real value) is computed with the formula of 3.2.3.8.1, i.e. :

$$RRx = \frac{D2VTx - O2DVTx}{2VRy - O2VRy} + 1$$

with absolute accuracy of +/- 1K.

UR-3.1.12-4.2: The new gain channel y is selected in the following two cases depending on the current gain selection

case y = HIGH (corresponding to temp range 60k-110k)

$\underline{\text{case y} = LOW}$  (corresponding to temp range 100k-330k)

NOTE: this is only the  $\frac{loqical}{loqical}$  gain selection to be computed before the  $\frac{loqical}{loqical}$  gain selection of UR-3.2.3.8.2.1 step 5 is performed.

UR-3.1.12-4.2.1: At power-on reset the y gain shall be set to LOW.

UR-3.1.12-5 The above timings may be changed during the design within +- 0.1 sec and must be performed with a tolerance of 10 msec.

The current generator shall be on 100 msec max.

UR-3.1.12-6

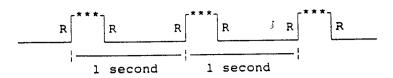

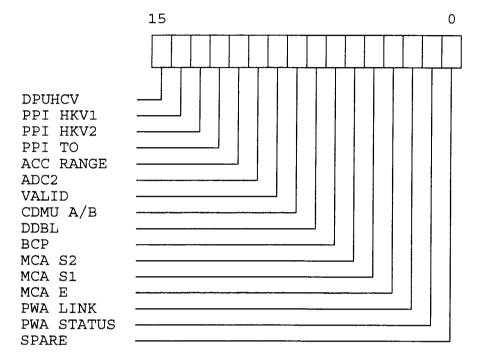

The sequence of 4 measurement (one for each HASI-DPU-SW