## **SPIRE DRCU Programme Review**

4 March 2003, SAp, Saclay

**Review Board Report**

SPIRE-UCF-REP-001573

**Annexes**

#### Annex A

#### **List of Participants**

| Jean-Louis | Augueres    | CEA                  |  |

|------------|-------------|----------------------|--|

| Jean-Paul  | Baluteau    | LAM                  |  |

| Yvan       | Blanc       | CNES                 |  |

| Christophe | Cara        | CEA                  |  |

| Ray        | Carvell     | PPARC                |  |

| Riccardo   | Cerrulli    | IFSI                 |  |

| John       | Delderfield | RAL                  |  |

| Jean       | Fontignie   | CEA                  |  |

| Matt       | Griffin     | Cardiff University   |  |

| Astrid     | Heske       | ESA                  |  |

| Filippo    | Marliani    | ESA                  |  |

| Karine     | Mercier     | CNES                 |  |

| Michel     | Mur         | CEA                  |  |

| De Antoni  | Philippe    | CEA                  |  |

| Frederic   | Pinsard     | CEA                  |  |

| Diminique  | Pouliquen   | LAM                  |  |

| Eric       | Sawyer      | RAL                  |  |

| Bruce      | Swinyard    | RAL                  |  |

| Henri      | Triou       | CEA                  |  |

| Laurent    | Vigroux     | CEA                  |  |

| Chris      | Whitford    | Leicester University |  |

#### Annex B List of Documents reviewed

| title                                          | doc number              | actual issue   | status                   |

|------------------------------------------------|-------------------------|----------------|--------------------------|

| Management plan for the Herschel project.      | SAp-FIRST-JLA-0038-01   | 4.0 23/01/2003 | ok                       |

| DRCU & WIH Development Plan                    | SAp-SPIRE-JLA-0047-01   | 4.0 29/01/2003 | ok                       |

| SPIRE product tree                             | SAp-SPIRE-DR-0094-03    | 1.0 21/01/2003 | ok                       |

| WBS Herschel                                   | SAP-FIRST-DR-0043-01    | 2.1 30/11/2001 | ok                       |

| WBS SPIRE                                      | SAP-FIRST-DR-0045-01    | 2.1 30/11/2001 | ok                       |

| SPIRE DRCU QM1master schedule                  | SAp-FIRST-DR-105-01     | 1 18/02/2003   | ok                       |

| DRCU Specifications document                   | SAp-SPIRE-Cca-0025-00   | 1.0 14/02/2003 | ok                       |

|                                                | (SPIRE-SAP-PRJ-000461)  |                |                          |

| DRCU ICD                                       | SAp-SPIRE-Cca-0075-02   | 1.0 14/02/2003 | ok                       |

|                                                | (SPIRE-SAP-PRJ-000451)  |                |                          |

| DRCU DPU ICD                                   | SAp-SPIRE-Cca-0076-02   | 1.0 14/02/2003 | ok                       |

|                                                | (SPIRE-SAP-PRJ-001364)  |                |                          |

| DCU design document                            | SAp-SPIRE-FP-0063-02    | 0.3 18/02/2003 | ok                       |

| Test plan DAQ IF                               | SAp-SPIRE-FP-0067-02    | 0.1 draft      | ok                       |

| Test plan BIAS                                 | SAp-SPIRE-FP-0066-02    | 0.1 draft      | ok                       |

| Test plan LIA P                                | SAp-SPIRE-FP-0064-02    | 0.1 draft      | ok                       |

| Test plan LIA S                                | SAp-SPIRE-FP-0065-02    | 0.1 draft      | ok                       |

| SPIRE test configuration                       | SAp-SPIRE-LD-0015-01    | 3.0 08/2001    | to be provided at review |

| FPU simulator specs for DCU / SCU test         | SIG-SPIRE-PdA-0030-01   | 03 14/02/2003  | ok                       |

| SPIRE LTU specifications                       | SAp-SPIRE-FD-0071-02    | 1.0 22/04/2002 | ok                       |

| DRCU AIV Plan                                  | SAp-SPIRE-HT-0082-02    | 2.0 03/02/2003 | ok                       |

| DRCU EM/QM1 preliminary test plan              | SAp-SPIRE-HT-0088-02    | 0.1 14/02/2003 | ok                       |

| SCU design document                            | SEDI-SCU-MM-2002-1      | 0.7 17/02/2003 | ok                       |

| PSU SPIRE specification                        | SAp-SPIRE-DS-012-02     | 1.1 11/12/2002 | ok                       |

| PA Plan                                        | SAP-GERES-Flo-436-00    | 1.0 07/11/2000 | ok                       |

| DPL                                            | SAp-SPIRE-NC-0061-02    | 1.0 13/02/2003 | ok                       |

| DML                                            | SAp-SPIRE-NC-0060-02    | 1.0 13/02/2003 | ok                       |

| DMPL                                           | SAp-SPIRE-NC-0100-02    | 1.0 13/02/2003 | ok                       |

| DCL                                            | SAp-SPIRE-VM-0098-02    | 14 10/02/2003  | ok                       |

| Synthesis note about DRCU FMEA and reliability | SAp-SPIRE-JF-0099-03    | 0.1 10/02/2003 | ok                       |

| WCA (and derating??)                           | will be performed later |                |                          |

# Annex C Review Meeting Presentations

## DRCU Programme Review CEA, Saclay 4 March 2003

## Objectives and Key Issues for the Review Matt Griffin

**DRCU Programme Review**

SAp, Saclay

4 March 2003

1

#### **Objectives**

- 1. Close out of the DRCU documentation review (= DDR), with special attention to interfaces

- 2. Review the DRCU development plan and schedule with respect to the instrument delivery schedule, with the aim of maintaining on-time delivery of the instrument PFM

- Demonstrate that the risks associated with the warm electronics programme are understood and can be controlled

- 4. Consider the necessary resources and management/ communication practices to allow the development plan to be effectively implemented

- Prepare for and cover most relevant issues for the instrument IHDR (to take place in July), which should then be rather routine for the DRCU)

**DRCU Programme Review**

SAp, Saclay

4 March 2003

2

#### **Review Board**

SPIRE Project Matt Griffin (chair)

Bruce Swinyard Eric Sawyer John Delderfield

IFSI Riccardo Cerulli

ESA Astrid Heske

Filippo Marliani

PPARC Ray Carvell

CNES Yvan Blanc

**Experts** Kees Wafelbakker

**Chris Whitford**

3

DRCU Programme Review SAp, Saclay 4 March 2003

**Agenda** Introduction and logistics 9:10 10 Jean-Louis Augueres Objectives and key issues for the review **Matt Griffin** 9:10 9:25 15 9:25 9:40 15 Instrument overview **Bruce Swinyard** 10:00 20 DRCU design overview Christophe Cara 9:40 10:00 15 DCU Frederic Pinsard 10:15 10:35 Coffee 10:15 20 10:35 10:50 15 SCU Michel Mur 10:50 11:05 15 MCU **Dominique Pouliquen Power Supply Specification Dominique Schmitt** 11:05 11:20 15 11:20 11:35 15 DDR close-out Eric Sawyer Eric Sawyer 11:35 **Instrument Development Plan and Schedule** 11:55 20 11:55 12:10 15 Instrument electronics AIV plan Eric Sawyer DRCU AIV plan Henri Triou 12:10 12:30 20 12:30 13:00 30 Questions and clarifications 13:00 14:30 90 Lunch **DRCU** Development and Procurement Plan 14:30 14:50 20 Jean-Louis Augueres Institute staffing and management 14:50 15:00 10 Jean-Louis Augueres 15:00 15:30 30 Questions and clarifications 15:30 20 15:50 15:50 **Review Board meeting** 16:50 60 16:50 17:00 Review Board feedback **Meeting End** 17:00 **DRCU Programme Review** SAp, Saclay 4 March 2003

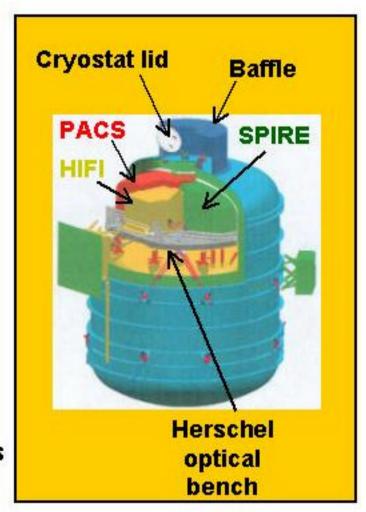

#### **SPIRE Instrument Overview**

**Bruce Swinyard**

RAL

#### **Instrument Design Drivers**

- Photometer (200-670 microns)

- Deep mapping of extra-galactic sky with highest efficiency and largest possible field of view

- Multi-band coverage with simultaneous observation

- Point and compact source observation with high efficiency

- Spectrometer (200->610 microns)

- Sensitivity optimised for point/compact source spectroscopy

- Imaging spectroscopy with maximum available field of view

- Wide wavelength coverage

- Variable spectral resolution (few x 10 to few x 100)

#### Both

- Thermal background dominated by the Herschel telescope

- Simplicity, affordability, reliability, ease of operation

- Complementary to other Herschel instruments and other facilities

#### **Instrument Summary**

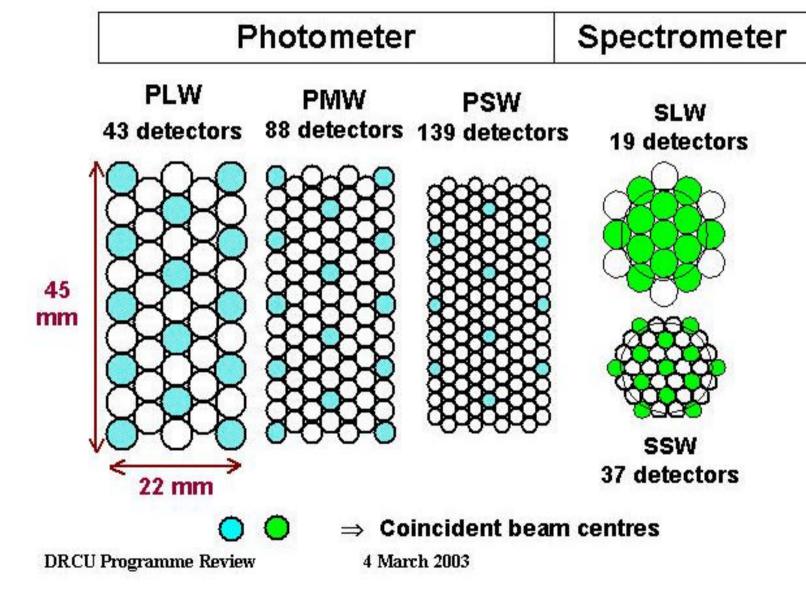

- 3-band imaging photometer

- 250, 360, 520 μm (simultaneous)

- λ/Δλ ~ 3

- 4 x 8 arcminute field of view

- Diffraction limited beams (17, 24, 35")

- Imaging FTS

- 200 670 µm

- > 2 arcminute field of view

- $\Delta \sigma$  = 0.4 cm<sup>-1</sup> (goal 0.04 cm<sup>-1</sup>) ( $\lambda / \Delta \lambda \sim 20$  - 100 (1000) at 250  $\mu$ m)

- Design features

- Sensitivity limited by thermal emission from the telescope (80 K;  $\varepsilon$  = 4%)

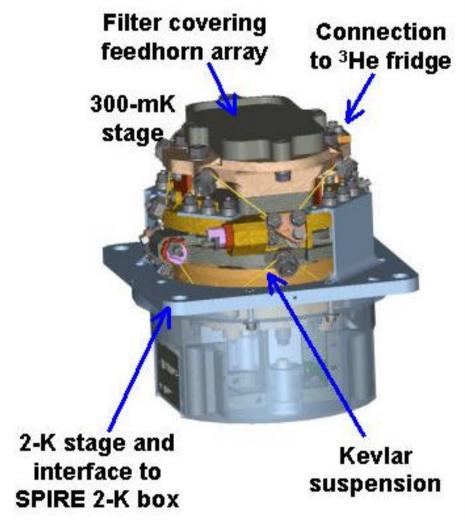

- 3He cooled detector arrays (0.3 K)

- Feedhorn-coupled spider web NTD bolometers

- Minimal use of mechanisms

- Beam steering mirror, FTS mirror drive

- No on-board data processing

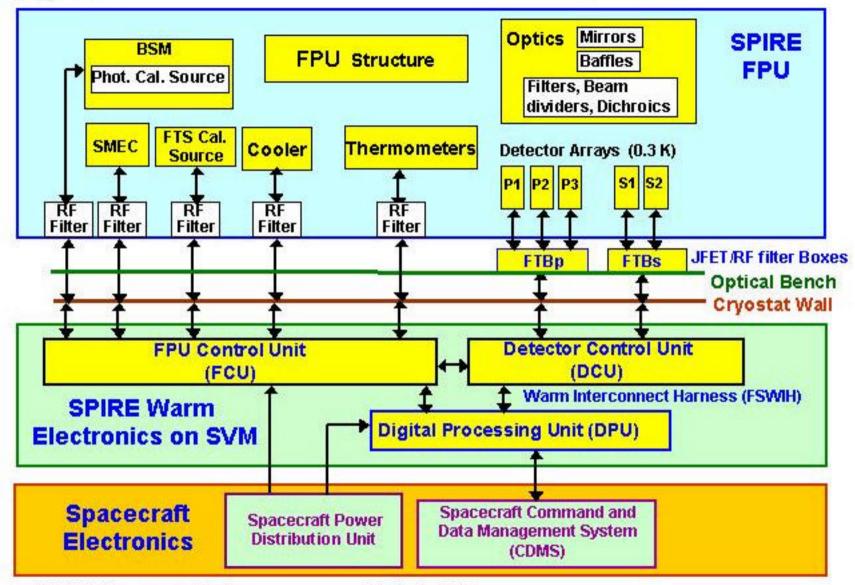

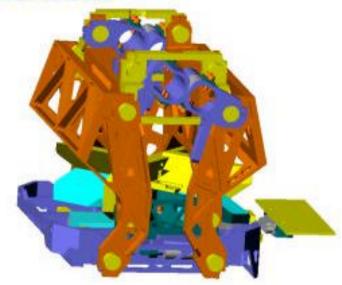

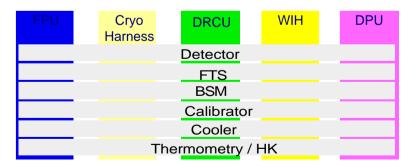

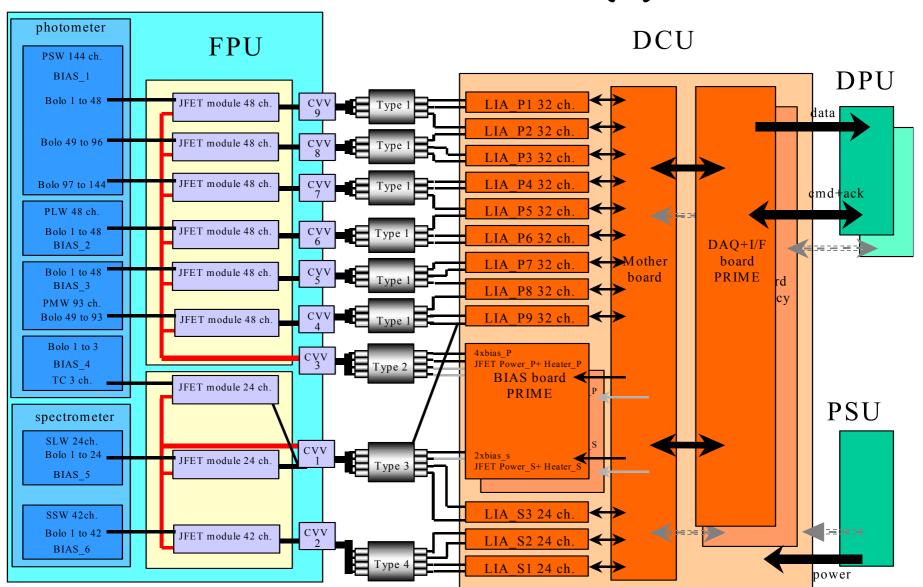

## **SPIRE Block Diagram**

#### **Focal Plane Unit**

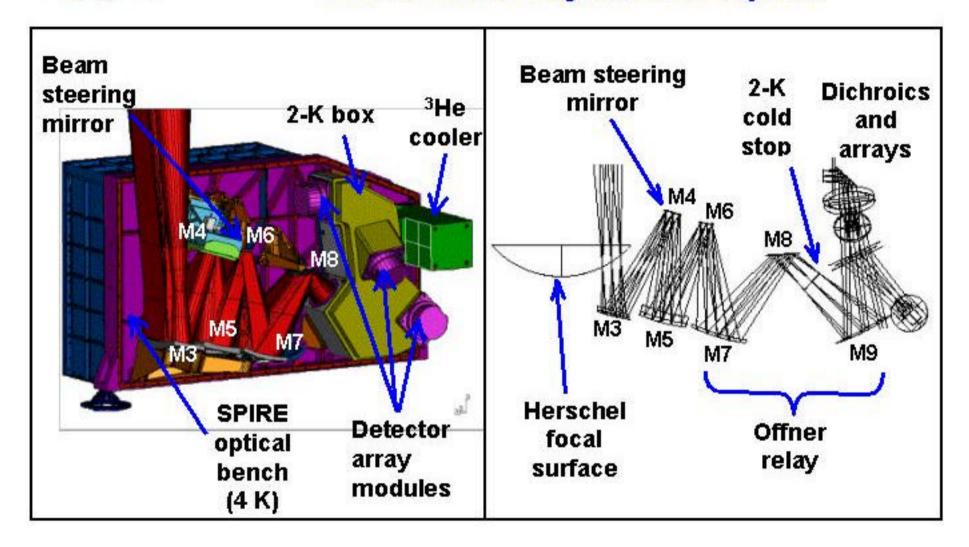

## **Photometer Layout and Optics**

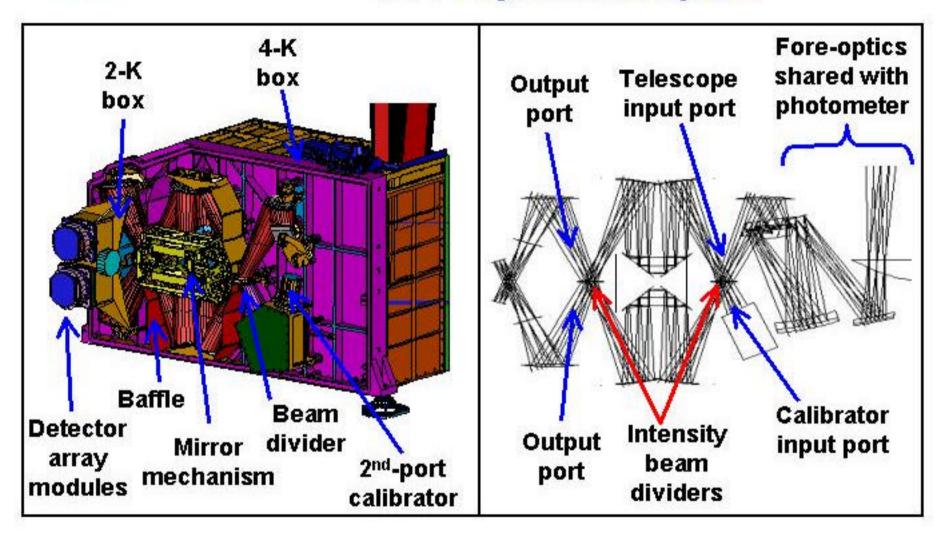

## **FTS Layout and Optics**

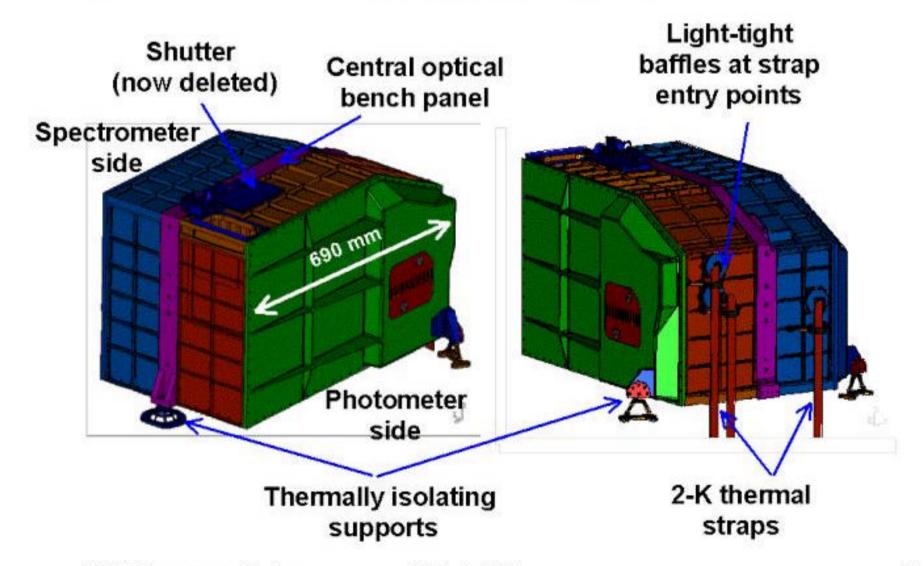

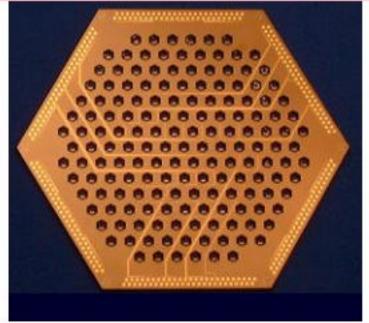

#### 2-K Enclosures for Detector Modules

#### Photometer

Spectrometer

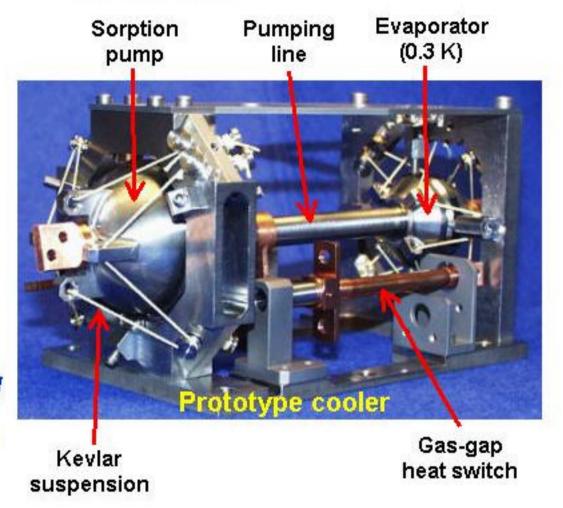

#### 3He Cooler

- Cold stage temp.

< 280 mK</li>

- Hold time > 46 hrs

- Cycle time < 2 hrs</li>

- Average load on <sup>4</sup>He tank < 3 mW</li>

- Heat lift provided to detector arrays > 10 μW

- Gas-gap heat switches (no moving parts)

- Driven by SCU DPU controls operations

#### **FTS Mechanism**

- Double parallelogram with toothless gear

- Movement range –0.3 to 3.5 cm

- Measurement of position by optical encoder with high resolution 10 nm

- Over part of range have backup LVDT with 100 nm resolution

- Signal conditioning; motor drive and speed control is done by MCU

- Start; stop and movement range controlled by DPU

## **FTS Observing Modes**

- Continuous scan:

- Mirror scan rate = 0.5 mm s<sup>-1</sup>

- Signal frequency range = 3 10 Hz

- Calibrator in 2<sup>nd</sup> port nulls telescope background

- Step-and-integrate:

- 2<sup>nd</sup> port calibrator is off

- Mirror stepped with integration at each position

- BSM chops on sky

- Point source spectroscopy/spectrophotometry

- Telescope pointing fixed

- Background characterised by adjacent pixels

- Imaging spectroscopy

- Beam steering mirror adjusts pointing between scans to acquire fully-sampled spectral image

#### **Beam Steering Mirror**

- Two axis mechanism

- Chop axis has +-2.5 degree throw at up to 2 Hz

- Jiggle axis has +-0.5 degree throw at up to 0.5 Hz

- Basic control done in MCU – DPU controls timing

#### **Calibration Sources**

- Two calibration sources are used – SCAL and PCAL

- PCAL mounted on the BSM

- Heaters and thermistors conditioned by SCU

- Timing and temperature control done using DPU

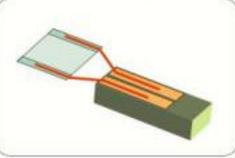

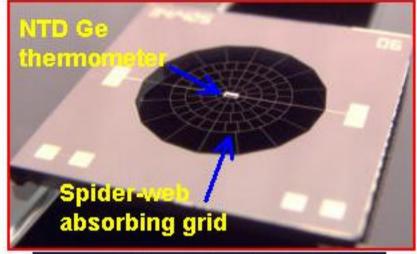

#### NTD Ge Bolometer Arrays (Caltech/JPL)

- NEP ~ 3 x 10-17 W Hz-1/2

- 120-K Si JFET readout

- 1/f noise knee < 100 mHz</li>

#### Detector Arrays (2Fλ Feedhorns)

## **Bolometer Array Module**

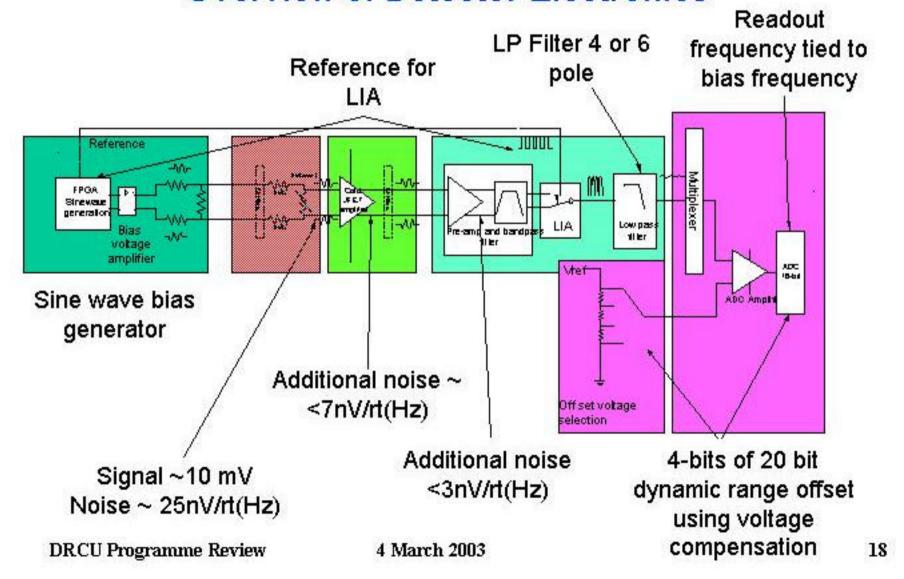

#### Overview of Detector Electronics

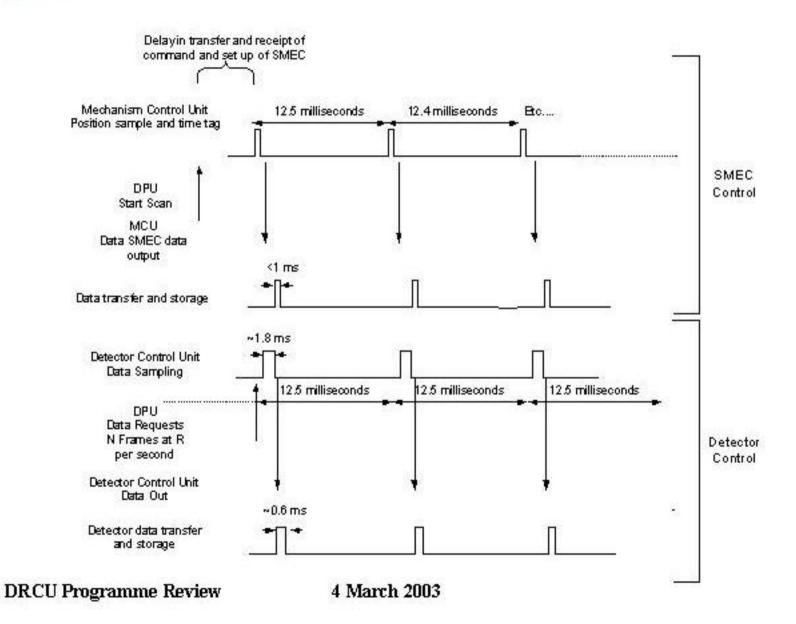

#### Instrument timing and control (S)

19

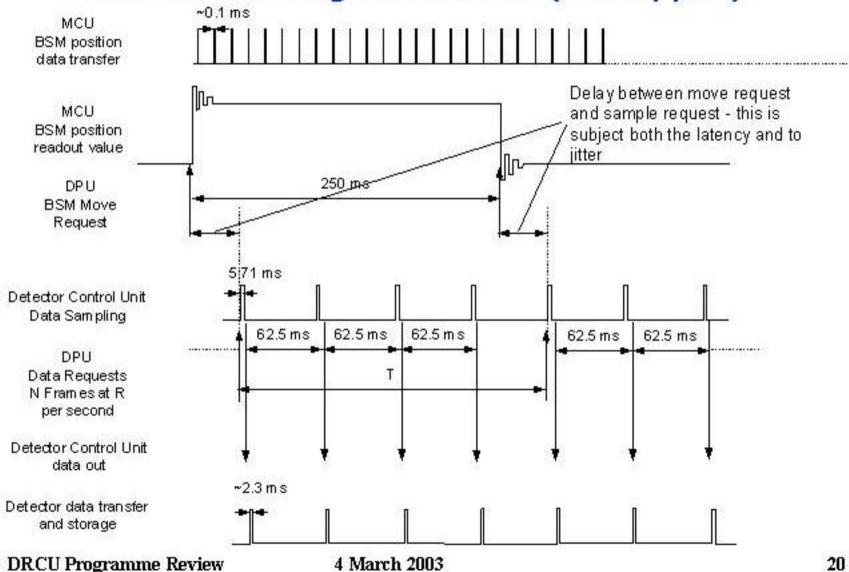

## Instrument timing and control (P chopped)

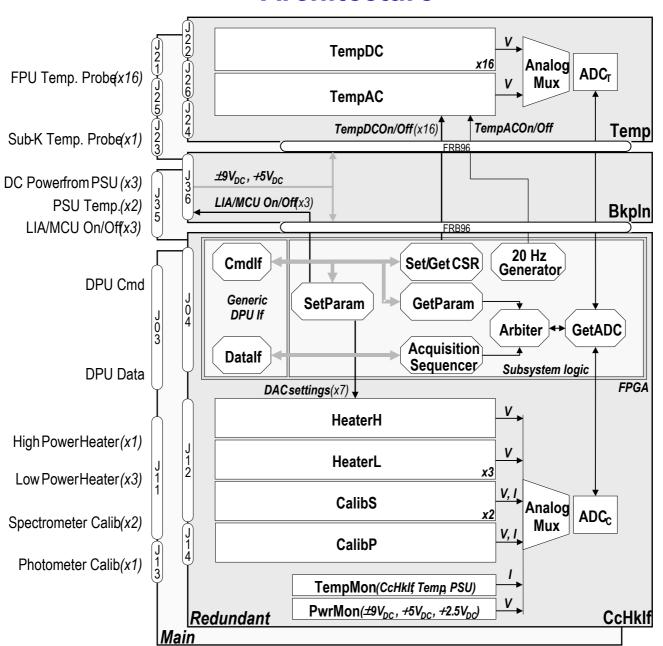

## **DRCU** Design

presented by C. CARA DRCU Engineer

contributors: V. MAUGUEN EEE engineer

T. TOURRETTE Mech. engineer

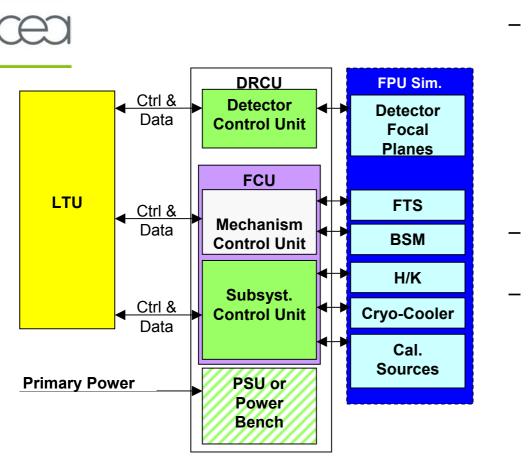

#### **Overview**

- The **DRCU** is a two box units:

- The FPU Control Unit (FCU) comprises

- The FTS and BSM associated electronics which constitutes the Mechanisms Control Unit (MCU)

- The Calibrators, cooler and thermometer associated electronics which constitutes the Subsystems Control Unit (SCU)

- The Power Supply Unit (PSU)

- The Detector Control Unit (DCU) comprises analog and digital electronics exclusively devoted to bolometers operation

- Additionally power distribution between boxes is achieved by means of harness:

- FCU to FCU (includes on/off commands for MCU & part of DCU)

- FCU to DCU (belongs to the WIH)

## Origin of Specifications

- from S/C:

- IID-A

- IID-B

- **2** from System level:

- Instrument Requirement Document

- Instrument Grounding Diagram

- Instrument Harness Definition

- **10** from sub-systems level:

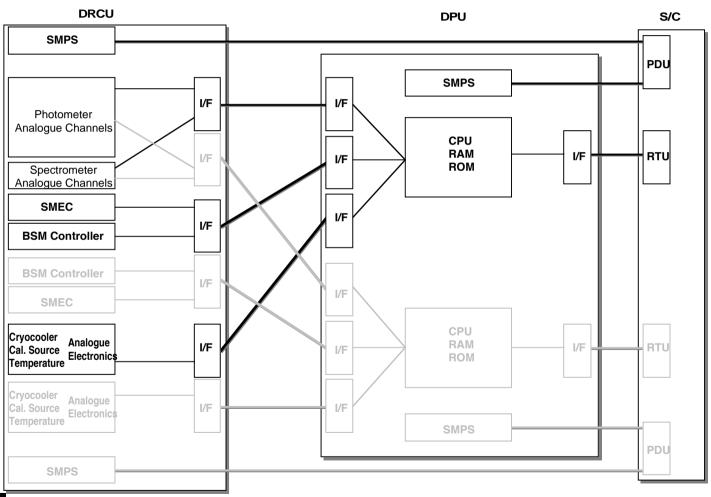

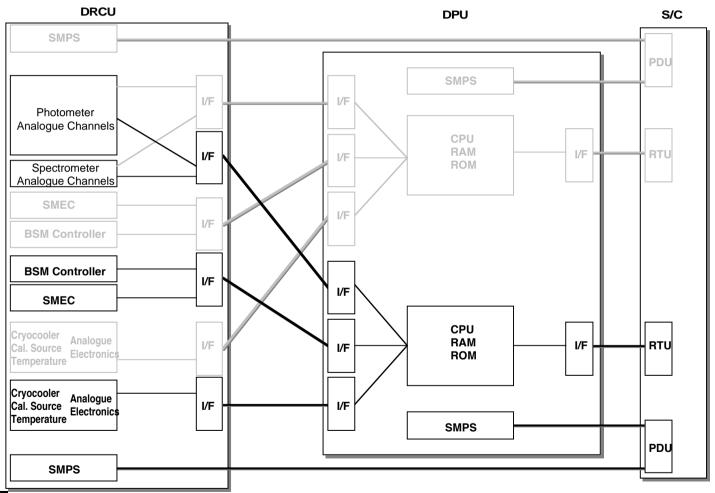

## Electrical Design (1)

Overall architecture:

3+1 electrically independent subunits

**DCU: Detector Electronics**

**MCU: FTS/BSM Electronics**

**SCU**: Calibrator/Cooler/Thermometry Electronics

+ PSU: DCU/MCU/SCU power supplies

Redundancy/Reliability

Architecture is driven by 2 main some

**Architecture is driven by 2 main constrains:**

- **Avoid as much as possible Single Point Failure**

- **cold redundancy is applied when possible**

- Limit failure propagation

- see DCU/LIA over-current protection

## Electrical Design (2)

#### main configuration

## Electrical Design (2)

#### redundant configuration

## Electrical Design (3)

#### **3** FPU / DRCU interfaces

- Most of interfaces are balanced

- Better rejection of external perturbations

- Common mode rejection optimized by balancing interface impedance where interface is single ended

#### **4** DRCU / DPU interfaces

- Data Interface timing optimization for 1 to 2.5 MHz operation

- DCU data packet pixel re-arranged

- MCU data packet redefined for more flexibility

- Command list updated for the 3 S/S

## Electrical Design (4)

- **6** Grounding scheme

- Finalized Q4/2002

- Goal: to limit propagation toward the FPU of noise sources in SVM (digital electronics, digital interfaces, DC/DC converters, ...)

- DRCU electronics is referenced to chassis at DCU and FCU level

- Board ground planes are connected to stiffeners

- Stiffeners/Case contact is low resistance

- Case/SVM panel is low resistance

- **⇒** Return path impedance for induced perturbation is minimized

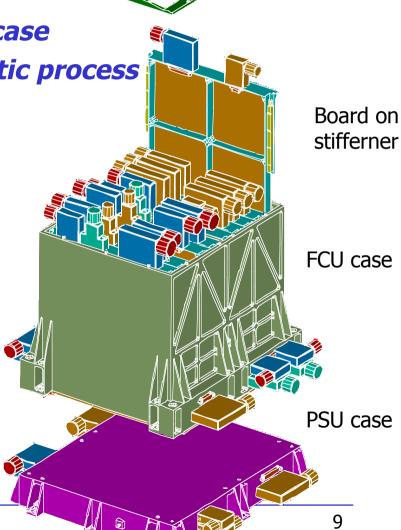

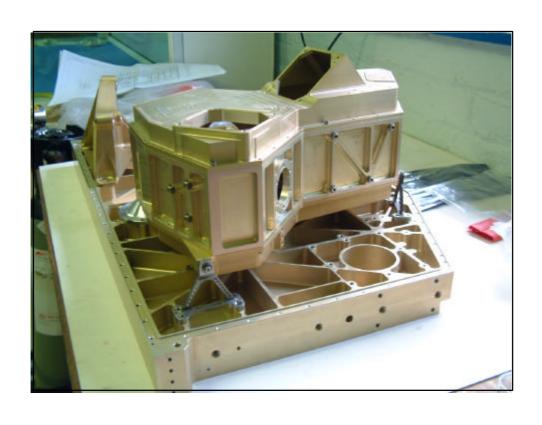

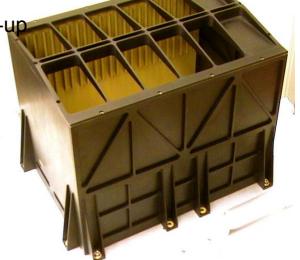

## Mechanical/thermal Design (1)

cover

1.5 mm Aluminum (+ stiffeners) case

Case assembly based on electrolytic process

Anodic oxidations treated surface

Boards mounted on stiffeners (screws + glue)

- **○** *Modeling shows:*

- Case eigen frequency: 500 Hz (>140 Hz / IID-A)

- Board frequency: 304 Hz

- Board deformation: ≤ 0.3 mm

6.040+0

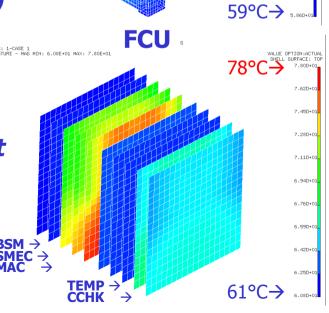

## Mechanical/Thermal Design (2)

Box design optimized for efficient heat transfer to SVM panel:

- Large contact area with panel:

- More than 28000 cm2 for DCU

- More than 100000 cm2 for FCU

- However FCU model shows:

- ✓ For 55°C panel/ambient temp. (qualif. level)

- $\checkmark \Delta t PSU = 6^{\circ}C$

- **○** Maximum box temp. = 65°C

- **Maximum board (**MCU/MAC) temp. = 78°C

Too close to derating rules (85°C for part case & 110°C for junction)

**⇒** To conservative estimation to be refined

# Interfaces with S/C

Allocated Budgets are almost meet:

SIZE DCU Design: 490x285x305 (mm)

*IID-B:* 494x289x305

FCU Design: 370x325x336 (mm)

*IID-B:* 370x325x336

MASS DCU Design: 15.67 kg

IID-B: 15.50 kg

FCU Design: 15.28 kg

IID-B: 15.00 kg

**DISSIPATION** DCU Design: 33.2 W

*IID-B:* 37 W

FCU Design: 47.6 W 80.8 W

IID-B: 42.9 W 79.9 W

Still to be confirmed by PSU contractor technical proposal (end of march)

# **EEE** parts

# Specification

- A DCL for DCU and SCU (CEA)

- ATP for LLI 01/03/02

- ATP for QM(2) 31/01/03

- ATP for FM active parts 03/02/03

- ATP for FM connectors 31/01/03

- ATP for passive parts pending

- A DCL for MCU (LAM)

#### Procurement

- All parts are procured through the First/Planck Parts

Procurement System

- Except one self-procured: operational amplifier (ref.OP400)

- Specific packaging for cost reduction and size optimization

- Procurement of dices (3000) from Analog Device

- Wafer Lot Acceptance (MIL-STD-883), Packaging, Qualification test (ESA/SCC900 level B), Up-screening (ESA/SCC 9000 level B), LAT 2

# **Critical Points**

- PSU late availability:

- Grounding scheme limits PSU injected current propagation

- **○** Need to specify accurately performance at interface level

- **⇒** PSU EM model delivered (temporally only) to perform capability tests with QM2 of DRCU

- Late test of the DRCU with CQM FPU:

- QM2 design starts before test result

- **○** Risk of late modification of QM2

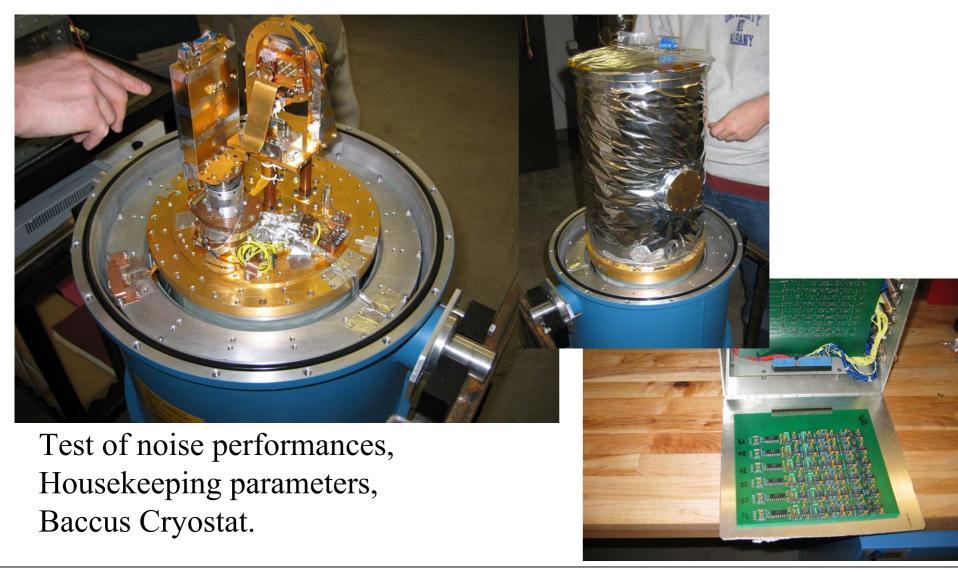

- ⇒ JPL test cryostat with a few bolometers available at CEA

- Board Operating temperature:

- Operating temperature too close to allowed maximum

- **Description** Model to be refined: PSU Δt, P<sub>dissip</sub>(board), ...

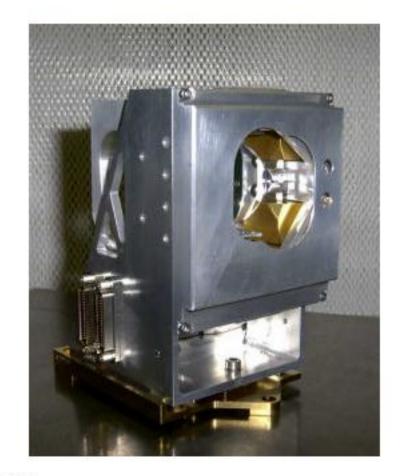

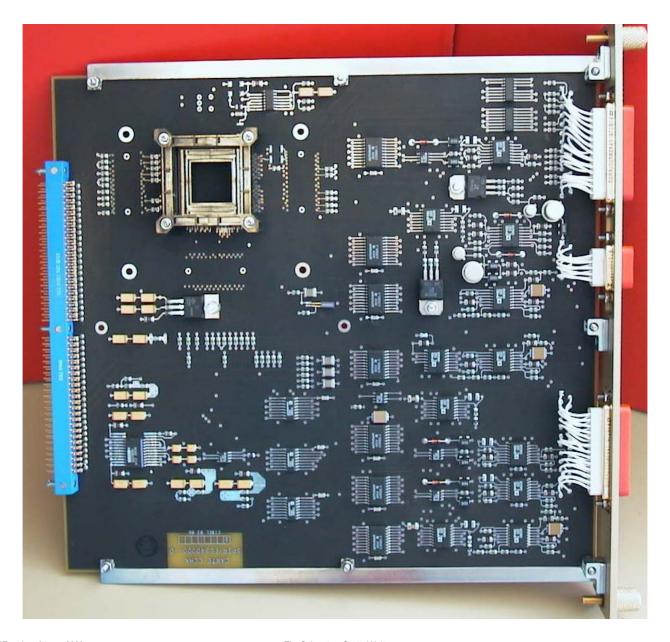

# Warm Electronic DCU Design

# FREDERIC PINSARD Service d'astrophysique CEA/DAPNIA pinsard@cea.fr

# DCU Overview (1)

- The DCU is a one-box unit:

- The Detector Control Unit comprises analog and digital electronics exclusively devoted to the bolometers' operation.

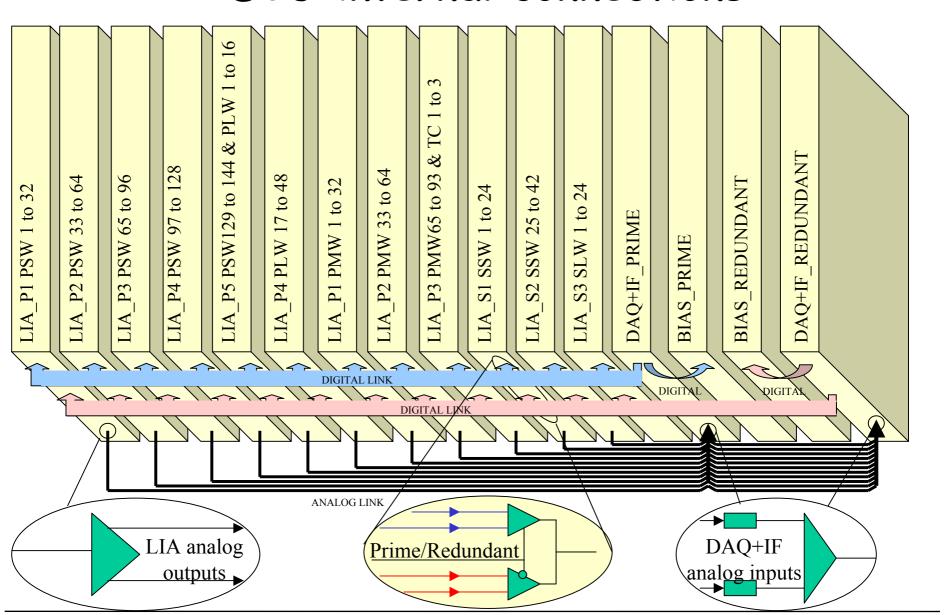

- In this box, 16 boards are connected on a back-plane printed circuit board.

- 9 LIA\_P boards process the photometer analog signals.

- 3 LIA S boards process the spectrometer analog signals.

- 2 BIAS boards (1 prime & 1 redundant) distribute the bolometers' bias and JFETs' supply.

- 2 DAQ+IF boards (1 prime & 1 redundant) digitize the signals and receive /decode the commands.

# DCU Overview (2)

# DCU internal connections

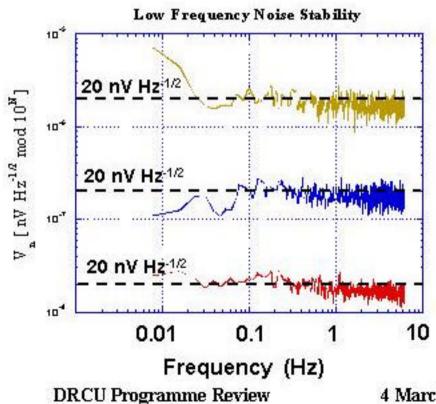

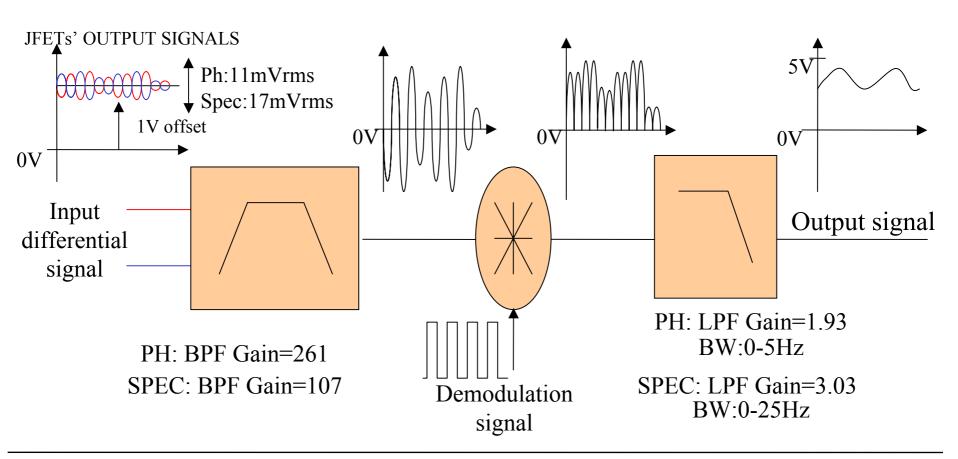

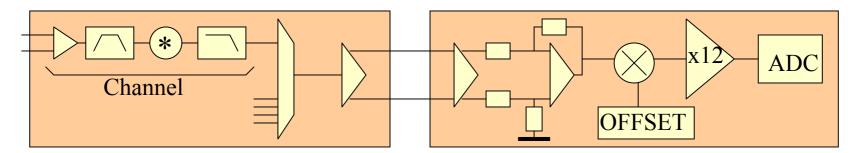

# LIA (1)

# Analog processing channels:

- Functions: to receive, amplify, demodulate & filter the bolometers' signals

- Total number 354 : 288 for the photometer + 66 for the spectrometer

# LIA (2)

# •QM1 measurement main results:

| BPF                          | Photometer |      | Spectrometer |       |

|------------------------------|------------|------|--------------|-------|

|                              | min        | max  | min          | max   |

| Gain                         | 260        | 265  | 113.2        | 115.5 |

| F <sub>-3dB</sub> low in Hz  | 34.4       | 35.1 | 35.2         | 35.9  |

| F <sub>-3dB</sub> high in Hz | 1453       | 1483 | 2673         | 2727  |

| Channel                     | Photometer |      | Spectrometer |      |

|-----------------------------|------------|------|--------------|------|

|                             | min        | max  | min          | max  |

| Gain                        | 446        | 449  | 308          | 315  |

| F <sub>-3dB</sub> low in Hz | 4.85       | 4.95 | 24.9         | 25.1 |

| CMR                         | -85dB      |      | -80dB        |      |

| Input noise in nVrms/√Hz    |            | 4.5  |              | 5.5  |

NOTE: 3 channels have flaws, but these problems are being investigated

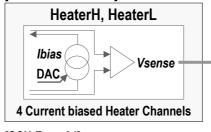

# BIAS

### • Bias generators:

- Functions: to generate sine biases for the bolometers and the DC biases for the JFETs and heaters

- Adjustable sine biases:

- Photometer: 1sine generator with 4 independent channel amplitudes

- Spectrometer: 1 sine generator with 2 independent channel amplitudes

- Adjustable DC biases:

- ➤ Photometer: 12 generators for the JFET + 1 for the heater with 7 buffers

- > Spectrometer: 3 generators for the JFET + 1 for the heater with 2 buffers

|                          | Sine bias |           | DC bias |     |              |

|--------------------------|-----------|-----------|---------|-----|--------------|

|                          | Ph/Spec   | TC        | Vss     | Vdd | heater       |

| Voltage range in Vrms    | 0 to 0.2  | 0 to 0.5  | 0 to -5 | 2.5 | 0 to -5V     |

| Frequency range in Hz    | 40 to 305 | 40 to 305 | DC      | DC  | DC           |

| Output current max in mA |           |           | 5mA     | 5mA | 2.5mA/buffer |

| Noise in nVrms/√Hz       | XX        | XX        | 250     | 200 | 250          |

# DAQ+IF

# • DAQ+IF functions:

Digitized data and transfer, timing cycle, command decoding, hk parameter transfer.

|                                  | Number | Parameter values | Range                          |

|----------------------------------|--------|------------------|--------------------------------|

| BIAS frequencies                 | 2      | 40 to1FF         | 40 to 305Hz                    |

| Sample frequencies               | 2      | 3 to FF          | $F_{BIAS}/3$ to $F_{BIAS}/256$ |

| Demodulation phases shifts       | 6      | 0 to FF          | 0 to 360°                      |

| Offsets                          | 354    | 0 to F           | 0 to 5V                        |

| Data transfer frequency          | -      | -                | 2.5Mb/s                        |

| HK& command transfer frequency   | -      | -                | 3125kb/s                       |

| Data ADC                         | 6      | -                | -2.5 to 2.5V (16 bits)         |

| Photometer picture acquisition   | -      | -                | 6ms                            |

| Spectrometer picture acquisition | -      | -                | 1.2ms                          |

| Frame number                     | 1      | 0 to FF          | 1 to 255 or continue           |

| Last gain stage on DAQ+IF (FUNC-02-7) Vrms                    | 2,51E-06 |

|---------------------------------------------------------------|----------|

| Offset stage on DAQ+IF (FUNC-02-06) Vrms                      | 2,68E-06 |

| Substractor stage on DAQ+IF (Analog receiver) Vrms            | 2,43E-06 |

| Differential receiver stage on DAQ+IF (Analog receiver) Vrms  | 2,15E-06 |

| Differential transmitter stage on LIA Vrms                    | 2,87E-06 |

| LIA photometer channel (FUNC-02-05,*-04,*-03,-02,*-01) Vrms   | 3,70E-06 |

| LIA spectrometer channel (FUNC-02-05,*-04,*-03,-02,*-01) Vrms | 6,13E-06 |

| ADC (DCU-FUNC-03) Vrms                                        | 5,80E-05 |

| Photometer input noise V/√Hz                                  | 8,20E-09 |

| Spectrometer input noise V/ √Hz                               | 6,57E-09 |

# STATUS

# • The DCU QM1 in progress

- Manufacturing and assembly of the LIA\_P2, LIA\_S2 and LIA\_S3

- Total noise measurement with the OP484 on DAQ+IF board

# The DCU QM1 future

- Test of the new LIA boards

- QM1 assembling

- QM1 testing alone

- Testing of the DCU QM1 with the test cryostat from JPL

- Testing of the DCU QM1 with simulators

**—** ...

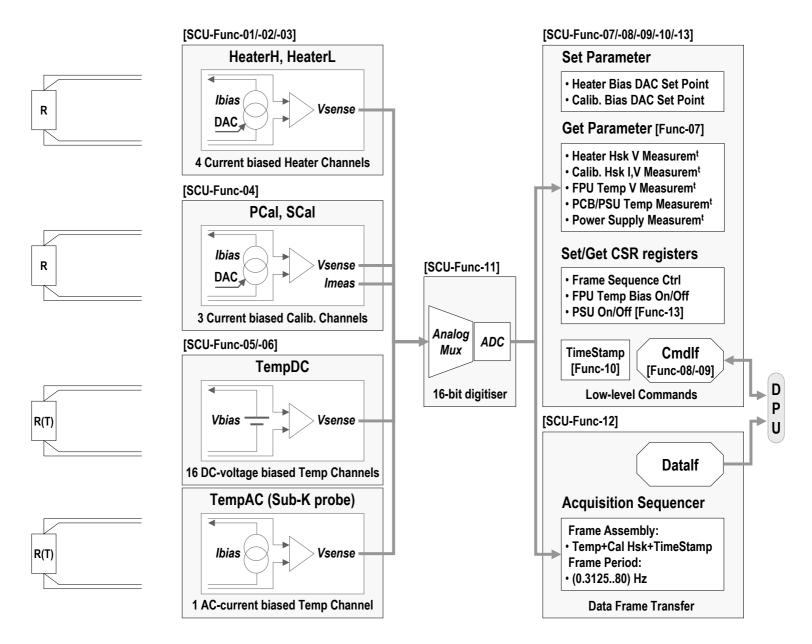

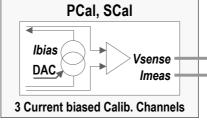

## The SCU

Functions

Architecture

DPU Interface

Subsystem logic

Analogue channels

Boards

Test strategy

Status

Michel MUR (CEA/DSMDAPNIA, 01 69 08 14 67, michel.mur@cea.fr)

#### Functional overview

#### **Architecture**

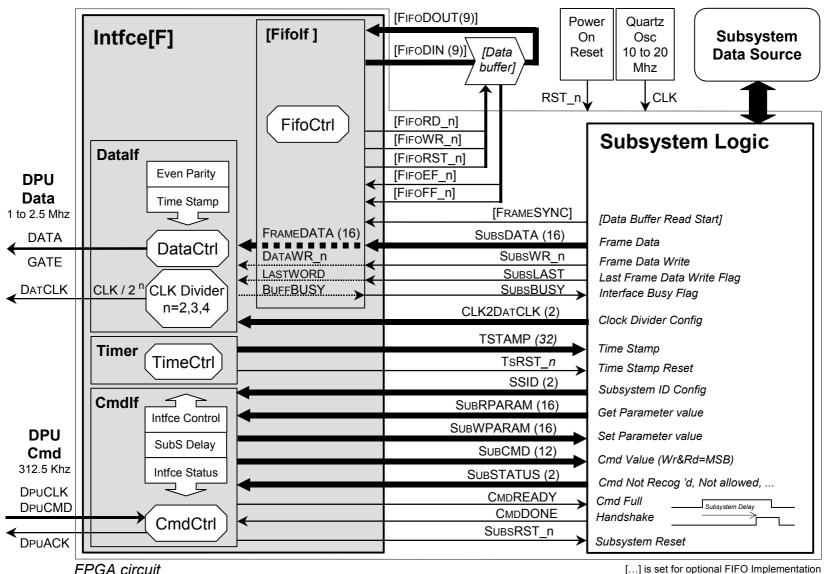

## Generic subsystem interface: concept

[...] is set for optional FIFO Implementation

## Generic subsystem interface: functions

#### Intfce

- Virtual component

- VHDL RTL for synthesis (ACTEL RT54SX32-S FPGA target)

#### Cmdlf

- Runs with DPU 312.5 kHz Clk alone

- Deserialises Cmds, serialises Ack

- Filters local/subsystem commands

- Supports simple, asynchronous handshake dialogue with subsystem

- Handles subsystem handshake timeout

#### Timer

Maintains Time Stamp

#### Datalf

- Runs from local oscillator

- Supports [1.. 2.5] MHz data rate

- Simple, synchronous subsystem word-based data interface

- Appends Time Stamp and parity to subsystem data

- Optional First In First Out subsystem buffer

- Synchronised by subsystem for frame transmission (Frame Sync)

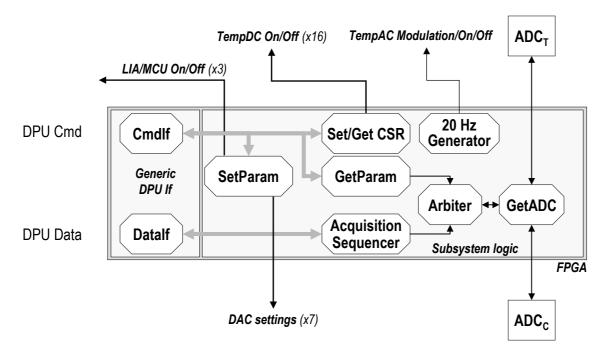

# SCU subsystem logic

#### Parameter access

Access to all parameters through Cmd interface (GetParameter)

#### Data frame sequence

- 0 (infinite),1 .. 31 frames per sequence

- 0.3125 .. 80 Hz frame frequency

- Word-per-word transmission (no frame buffer)

- Maximum analogue parameter collection interval: less than 6 ms

- Pseudo-random test pattern capability

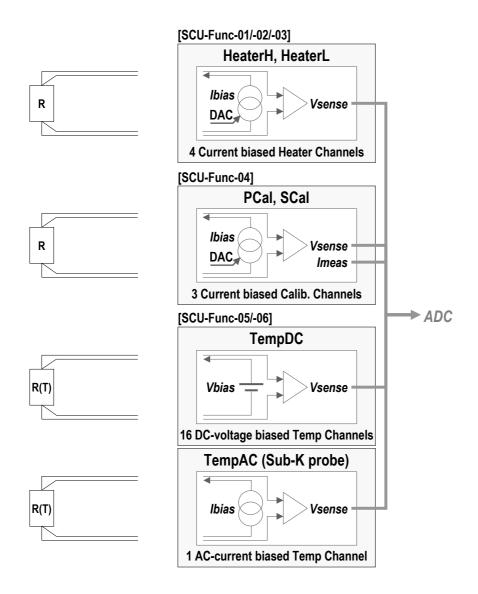

## Analogue measurements

$$I_{bias} = a * DAC + b$$

$ADC(V_{sense}) = a * V_{actual} + b$

$$I_{bias} = a * DAC + b$$

$ADC(V_{sense}) = a * V_{actual} + b$

$ADC(I_{meas}) = a * I_{bias} + b$

$$ADC(V_{\text{sense}}) = a/R + b$$

$$ADC(V_{sense}) = a * R + b$$

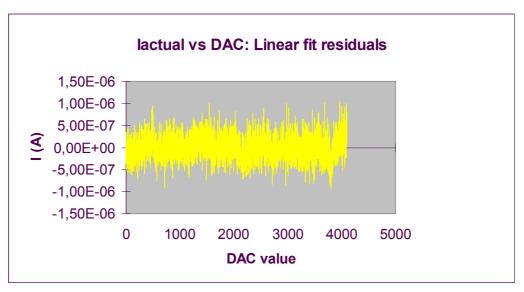

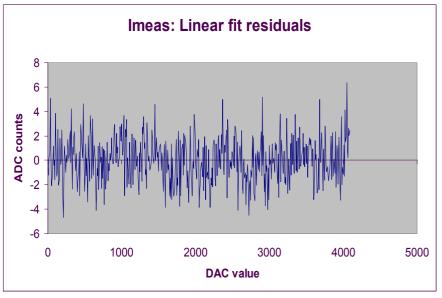

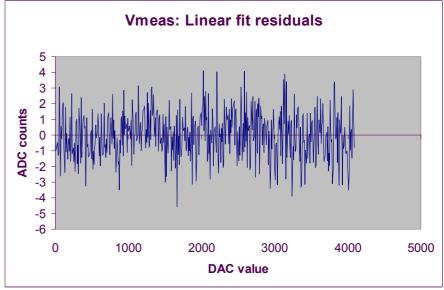

# Calibrator prototype: Linearity

#### Linearity test at 25°C

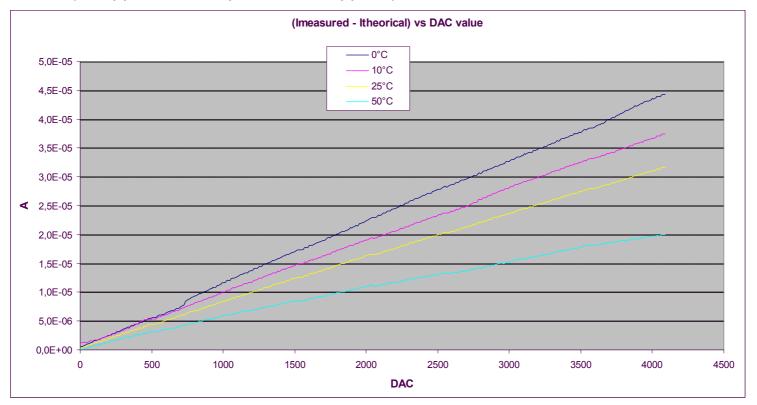

## Calibrator prototype: Stability

#### Variation with temperature

- 4% of the stability budget

- Prototype current variation: 25uA/50°C@9mA

- o corresponding relative dependence: < 60 ppm/°C.

- Specification for relative stability: < 5.E<sup>-3</sup>/h (maximum temperature drift: 3K/h).

- Without correction: <4% of the total stability budget</li>

- (180 ppm of the requested 5000 ppm/h).

## **Boards: Cchklf**

# **Boards: Temp**

#### Test: measurements

#### Loop over DAC values

#### Loop over R values

#### [SCU-Func-01/-02/-03]

#### [SCU-Func-04]

#### [SCU-Func-05/-06]

#### Linear regressions: Measure

- Slope (a)

- Intercept (b)

- Residuals

$$I_{bias} = a * DAC + b$$

$$ADC(V_{sense}) = a * V_{actual} + b$$

$$I_{bias} = a * DAC + b$$

→ ADC

$$ADC(V_{sense}) = a * V_{actual} + b$$

$$ADC(I_{meas}) = a * I_{bias} + b$$

$$ADC(V_{\text{sense}}) = a/R + b$$

$$ADC(V_{sense}) = a * R + b$$

1 AC-current biased Temp Channel

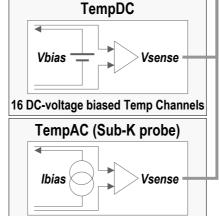

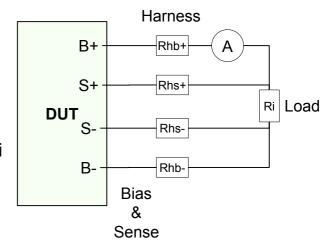

## Test: principle

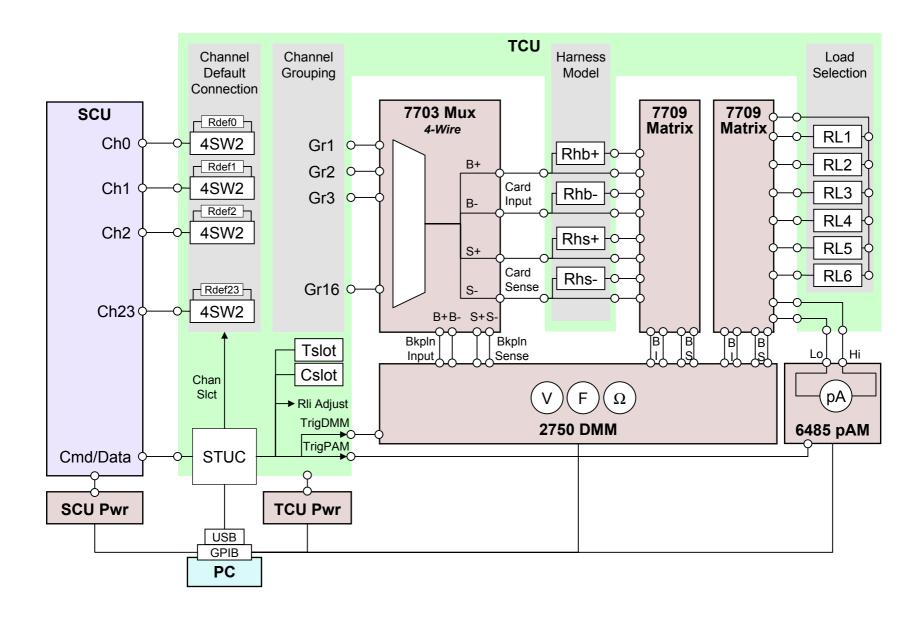

#### Generic circuit (all channels)

- Variable load for calibration of a 4-wire measurement circuit

- Possibility to insert/bypass Rh resistors (to model the harness resistance)

- Possibility to select one out of several reference loads Ri

- O Path to measure current in a separate ammeter

#### Matrix connections

- Rhb+, Rhb- inserted

- Rhs+ inserted

- Rhs- inserted

- R4 load selected

## QM2/FM Test: Automated setup

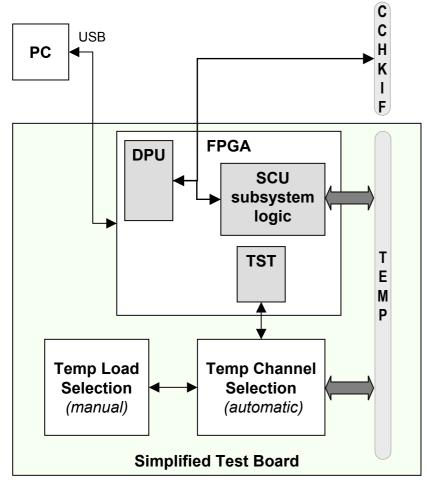

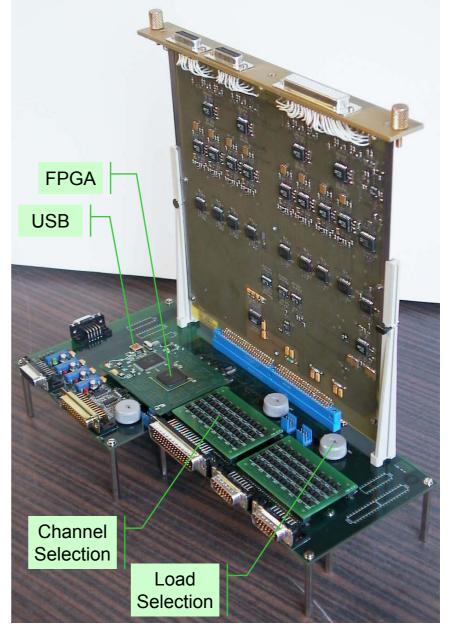

## QM1 Test: Simplified setup

- Direct test of Temp board

- O DPU host interface in FPGA

- O Nominal Subsystem logic in FPGA

- External Test of CchklF

- o fixed loads

## Status (QM1)

- Board design

- Completed

- FPGA design, simulation, Place & Route validation (Actel)

- Completed

- Test preparation

- Hardware (Simplified Test Board)

- ◆ Ready

- Software

- Primitives (Host commands)

- Completed

- ◆ Application (measurement loops)

- In progress

- Measurement analysis (simple linear regression analysis)

- « Manual » process for QM1

#### Test activity & report

o March-April 2003

# **Mechanisms Control Unit**

D. Pouliquen

Laboratoire d'Astrophysique de Marseille

#### **MCU**

The MCU controls the SMEC and the BSM mechanisms.

The MCU is designed and developed at LAM with the cooperation of UKATC for the BSM part and of CEA-Sap for the DRCU part.

- Based on a DSP 21020, with assembly language software

- Controls 3 axis: 1 for SMECm and 2 for BSM

The MCU comprises 6 boards mounted in the FCU:

- 2 Multi Axis Controller boards (nom+red)

- 2 Spectrometer MEChanism board (nom + red)

- 1 Beam Steering Mirror board (nom+red on the same board)

- 1 backplane board.

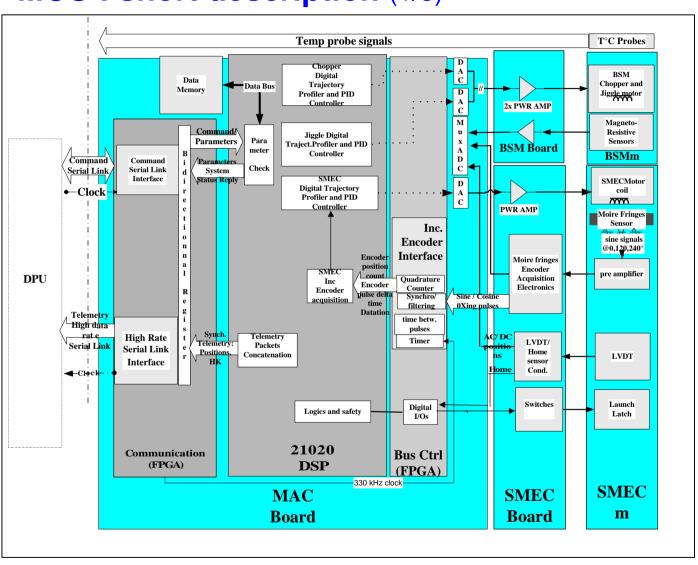

# MCU: short description (1/3)

- DSP 21020 + mechanism control software

- Interfaces with DPU = one FPGA for both the TM and the TC.

- One analogue board per mechanism to condition the signals to and from the mechanisms (position signals, actuator currents)

# MCU: short description (2/3)

#### **SMECm Optical Encoder Position Acquisition**

Calculated on the basis of the 3 sine optical encoder signals after pre-amplification, conditioning to be read directly by the DSP via a multiplexed 16 bits ADC for arctangent calculation.

#### **SMECm Optical encoder LED control**

Because of the possible decay of flux emitted by the optical encoder LED due to ageing, 8 possible current levels can be set by the MAC board through the digital I/O port (3bits encoding).

#### SMECm Degraded mode control using the LVDT

For R=100 travel (+/- 3.2 mm)

signals acquisition is done on the SMEC Board and digitised by a 16 bits multiplexed ADC converter

useful range of the LVDT measurement with nominal linearity = +/- 2.54mm extended at twice this length with poorer linearity performance.

#### SMECm Degraded mode control using the motor back emf

For a complete SMEC mechanism travel

Uses the mechanism stiffness law

permits a velocity control of the mechanism only.

# MCU: short description (3/3)

**BSM Position** = measured by magneto resistive signals **BSM Movement** = angular travel in two orthogonal axes. Performed with actuators **BSM Control** =

- digital conventional PID (3-term) controller with corrections for cross-coupling between axes- in the MAC Board.

- Each axis can move independently. Typically, a step command waveform is assumed, and above a certain amplitude (10% of peak), it is profiled to produce a sinusoidal acceleration demand.

- The movement with respect to time is profiled via stored parameters to give a minimum energy, minimum noise position change, particularly for step commands. In general the movements are repetitions of the same position/time profile.

- In addition, in the event of measured behaviour resulting in a fault diagnosis, some system backup procedures are available. Diagnosis of excessive position errors and analysis of recorded transient behaviour during operation can result in modifications to the control system by uploading different parameters.

# MCU: Design change since MCU DDR (Oct 2001) [1/3]

# > Addition of boards temperature measurements

One temperature sensor added on each nom and red card Total = 6 sensors (no sensor on the backplane)

# Method of SMEC mechanism speed control with the optical encoder revised:

the optical encoder zero crossing counting is done exclusively by software. It was previously done by hardware.

- => suppresses offsets adjustments in the hardware

- => simplifies the hardware

- => simplifies the control software

ECR issued and accepted

Modification being implemented

# MCU: Design change since MCU DDR (Oct 2001) [2/3]

# > Damping of the SMEC mechanism

One relay added that short circuits the coils when no power available

When one coil in use, the other one remains short circuited Provides damping to improve the mechanism control Prevents the mechanism from banging against the mechanical stop in case of sudden power failure

# > Suppression of the BSM launch latch

due to successful vibration tests of the BSM without launch latch

- => simplifies the BSM board

- => erases a problem with the SPIRE harness

# MCU: Design change since MCU DDR (Oct 2001) [3/3]

# > Introduction of a BSM damping for launch

The need is not clear. Complement of study under progress at UKATC.

# Introduction of a BSM damping for control

Control easier with little dampening => introduction of a resistance in the actuators coils circuit. Done on the QM1, perhaps suppressed on further models.

# Decisions concerning the BSM to be taken this week with UKATC and SPIRE system team

# **MCU**: Interfaces documents

- > DRCU ICD Sap-SPIRE-CCa-075-02 Issue 1.0, 14 Feb 2003

- => MCU / DPU, MCU / PSU and MCU / Mechanisms electrical interfaces

- => MCU command list

- > SPIRE Harness Definition Document, SPIRE-RAL-PRJ-000608 Issue 1.1, 8 July 2002

- => Mechanisms simulator electrical interfaces (pin out = mechanisms connectors pin out, Sub D connectors)

- > SPIRE FCU MICD, SPIR-MX-5200-000 Issue E, 26 Sep 2002

- => MCU Connectors position, reference axis, etc...

- > SPIRE Rack type LIA Plan d'interface, SPIR-MX-5110-000 Issue A, Oct 2001

- => MCU boards mechanical interfaces

# MCU: the models [1/2]

# > QM0 : for communication tests

- Built at LAM

- New model introduced for planning reasons

- Form & fit, electrical, command interface & flight functions Ok

- ALTERA FPGA including CEA DAPNIA Communication VHDL issue 0.4

- Commercial components, no redundancy

- Not suitable for mechanisms control

- Delivered with mechanisms simulator and cables

# QM1 : for CQM tests

- Built at LAM

- Same as QM0 plus mechanism control capability

- To replace the QM0 in the FCU QM1

# After QM1 delivery, the QM0 comes back to LAM and can be refurbished at QM1 level.

# MCU: the models [2/2]

# > QM2 : Used to qualify the electronics

- Sub contracted by LAM

- QM2 design = QM1 design

- Form & fit, electrical, command interface & flight functions Ok

- Military components, redundancy

- ACTEL FPGA including CEA FPGA Communication VHDL (black box) issue TBD

- Delivered with mechanisms simulator and cables

### QM2 to be used with FPU FM as FCU FM not available on time

## > FM and FS

- Complete flight models

- Sub contracted by LAM (same contract and contractor as for the QM2)

All MCU models to be delivered by LAM to CEA

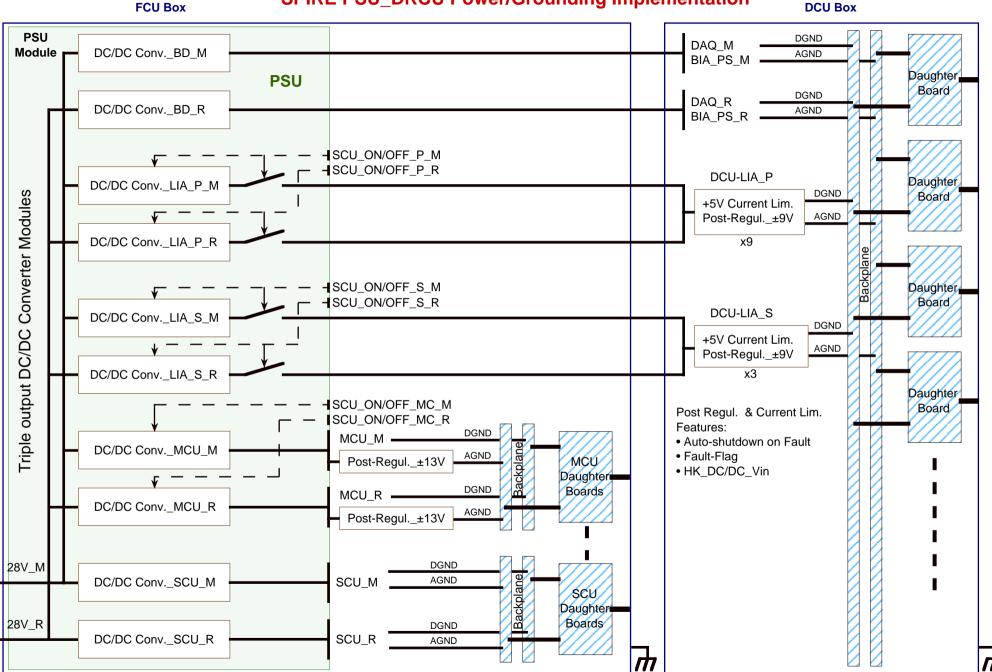

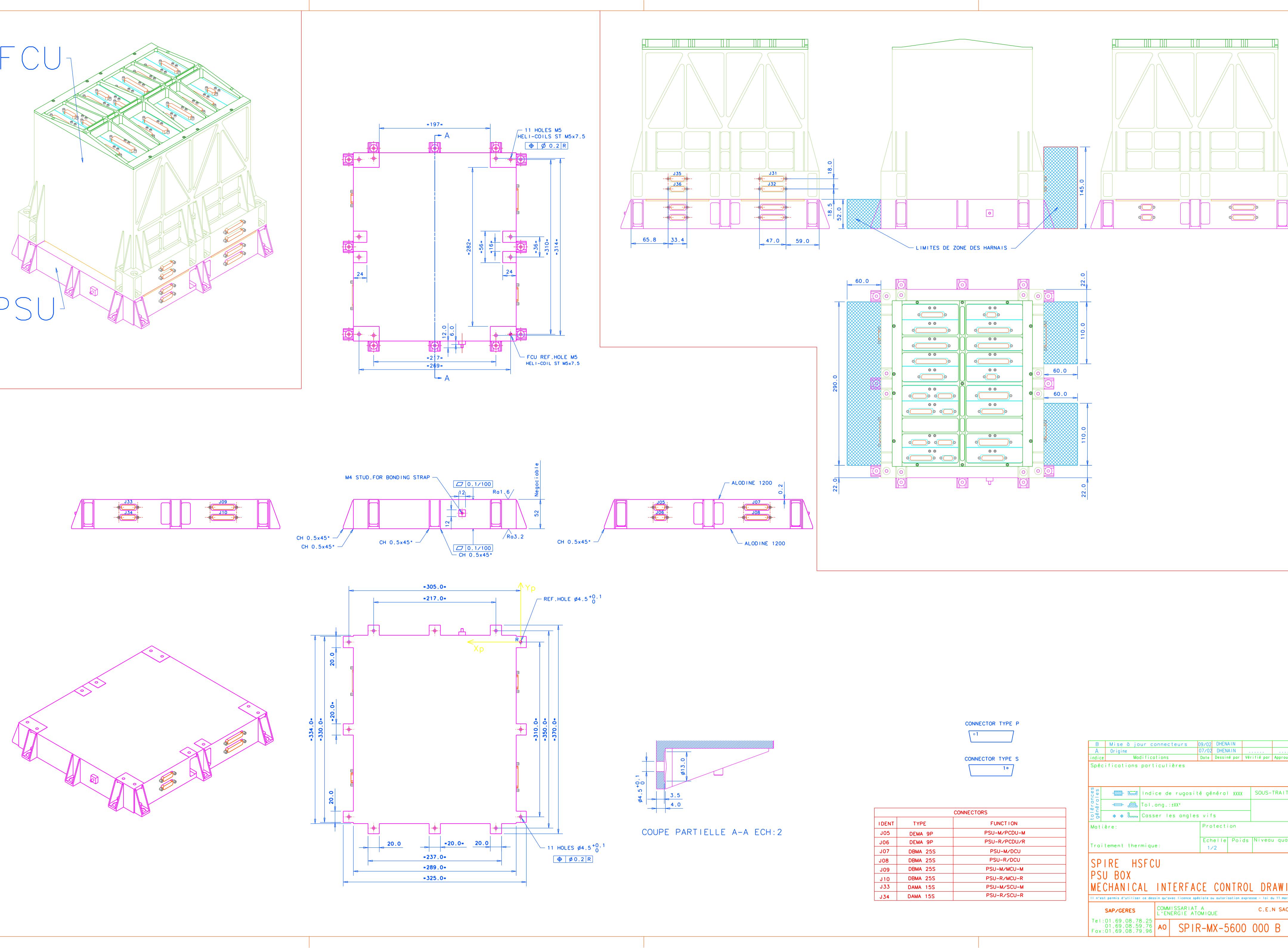

### **SPIRE PSU DRCU Power/Grounding Implementation**

# HERSCHEL—SPIRE FCU-PSU

### Model policy:

#### STM

- Will contribute to the qualification of the FCU box

- Secondary Power supplied by an external power bench

#### **EM**

- Not a deliverable item

- Compliant Mechanical and Electrical I/F

- Will be used by the contractor for verification purposes, test of corrective actions...

- Will be borrowed for electrical compatibility test at Saclay

#### **FM**

• Flight compliant

#### **Spare**

- PCB or part level

- FM repaired and tested at acceptance level within 3 weeks

### **Expected Schedule:**

- ITT in progress, first answers by the end of March

- Market rules completion and kick-off by the end of June (CEA-CCM calendar)

- FM delivery: kick-off + 14 months

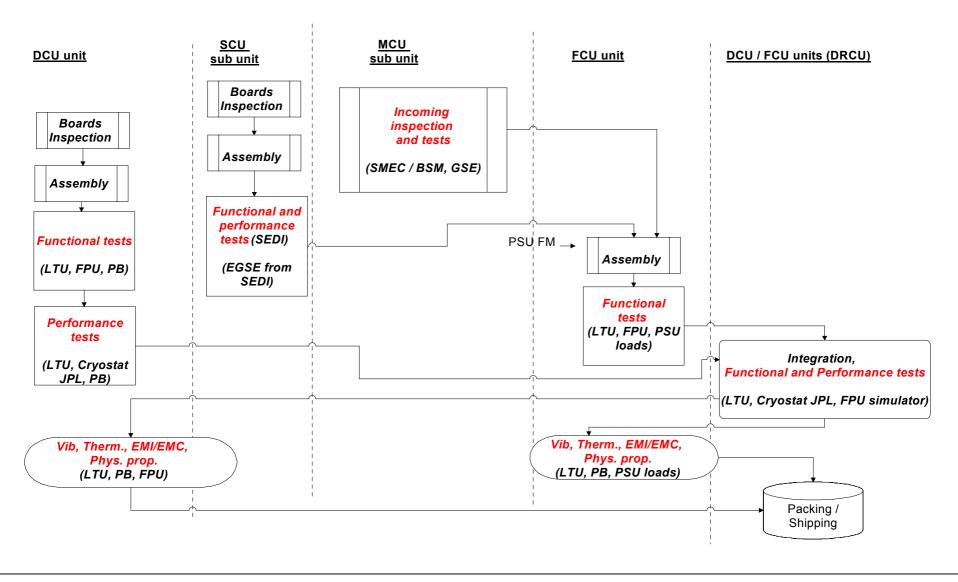

# AIV DRCU TEST PLAN

- OBJECTIVES (as defined in the development plan)

- To check Sub systems <u>Performances</u> and <u>Functions</u> at the appropriate level before integration into the instrument,

- To perform <u>Qualification</u> or <u>Acceptance</u> tests of all individual Sub-systems before integration into the instrument.

## MAIN STEPS

To fulfil the objectives, the AIV plan defines:

- the actions to be performed for each model following the model philosophy (STM, QM1, QM2 and FM),

- the sequencing of the actions performed on units for each model (Flow Charts),

- the detail of each AIV action together with the resources required (SADT diagrams),

- the kind of tests performed on each unit / sub unit to ensure test coherency (Test matrixes),

- the test equipments required for each test (harnesses, LTU, FPU, PB ...),

- the documentation (test plans, logbooks, NCR ...),

Henri TRIOU SPIRE AIV March 4th. 2003

SPIRE DRCU REVIEW March, 4th. 2003

### Classification of AIV actions

#### The AIV Actions consist in:

<u>Inspections</u> (concerns items delivered by subcontractor) that involves:

### **Incoming inspections**:

- Visual inspection to verify:

- Marking of the box and of the connectors, checking of the connector itself,

- Mechanical integrity of the box,

- Surface treatment status of the box,

- Review of the delivered documentation,

#### **Incoming tests:**

- Simplified functional tests.

### **Assembly** that involves:

- Visual inspection,

- Electrical interface verification to check the compatibility (electrical mass, Back Plane isolation ...),

- Mechanical assembly, Electrical tests,

- Simplified Functional tests

### **Integration of units** that involves :

- Visual inspection,

- Electrical interface verification to check the compatibility of units

- Electrical tests

**Functional / Performance tests** following the system and interface requirements

**Qualification / Acceptance tests** performed under environment conditions following the system and interface requirements

=> We then detail the AIV action flow charts for QM1, QM2 and FM models

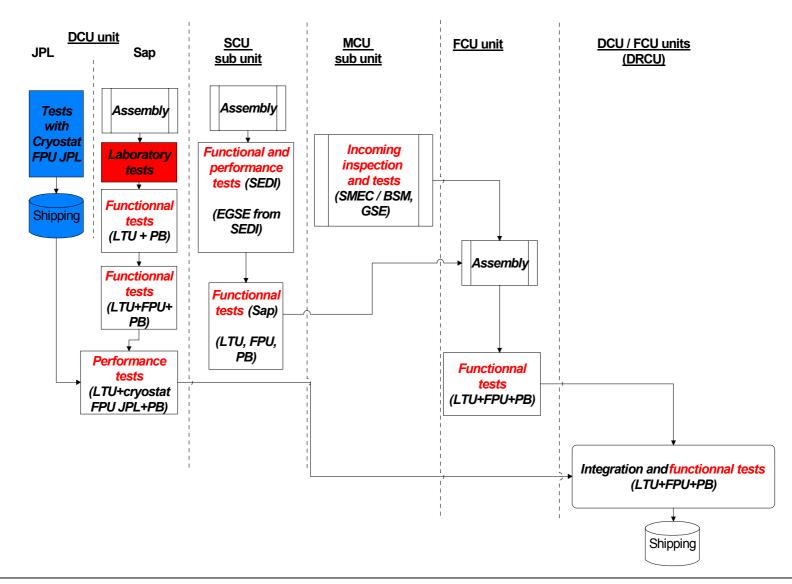

### DRCU QM1 model flow chart (QM1 = test mean for CQM)

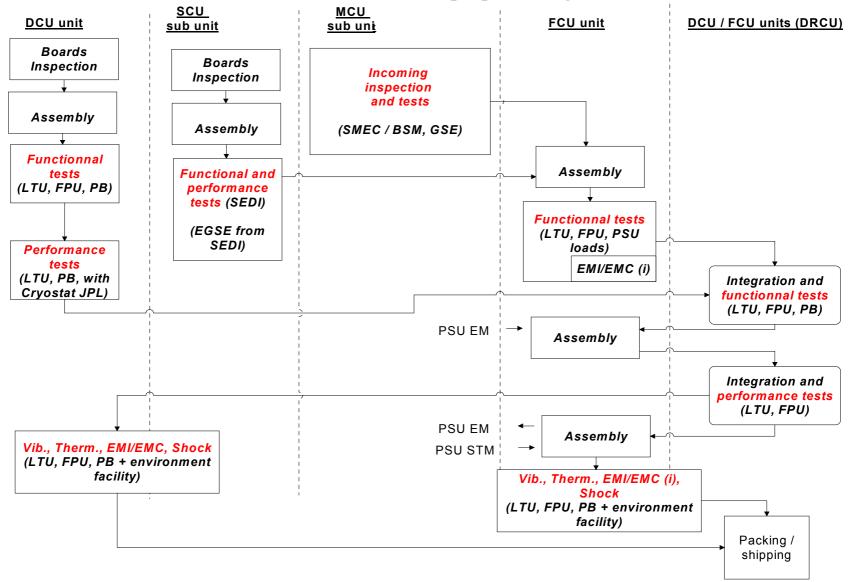

### DRCU QM2 model flow chart (QM2: to prepare integration)

### **DRCU FM model flow chart (For Acceptance tests)**

SPIRE DRCU REVIEW March, 4th. 2003

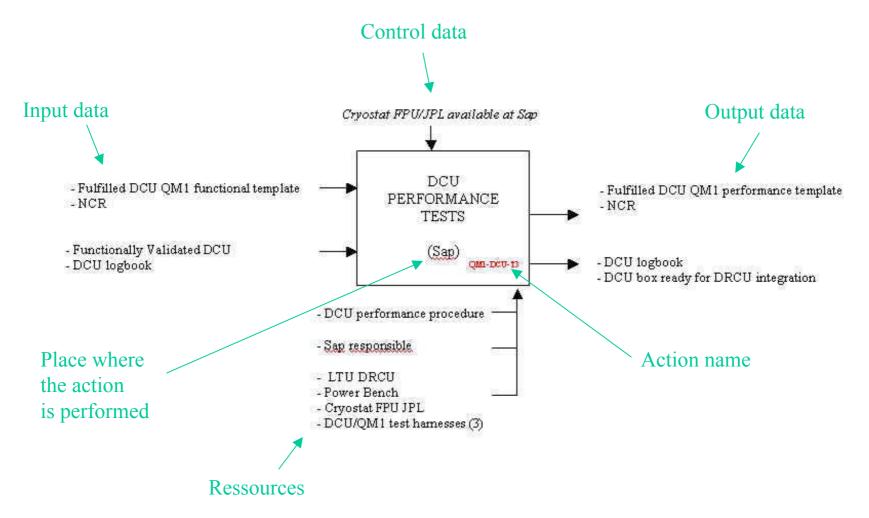

# SADT diagrams

SPIRE DRCU REVIEW March, 4th. 2003

### **Unit test matrix (DCU or FCU)**

| Test / Model                                                 | QM1     | QM2                | FM                            |

|--------------------------------------------------------------|---------|--------------------|-------------------------------|

| Inspection                                                   | A       | A                  | A(3)                          |

| Electrical tests                                             | Т       | T                  | T <sup>(3)</sup>              |

| Functional tests                                             | T       | T                  | T <sup>(3)</sup>              |

| Performance tests                                            | No Test | No Test            | No Test                       |

| Vibration tests (*) Qualification level Acceptance level     | No Test | T <sup>(2)</sup>   | T <sup>(3)</sup>              |

| Thermal balance tests                                        | No Test | No Test            | No Test                       |

| Thermal tests (*) Qualification level Acceptance level       | No Test | T <sub>V</sub> (2) | T <sub>V</sub> <sup>(3)</sup> |

| EMI/EMC tests (*)  Qualification level  Acceptance level     | No Test | T <sup>(0)</sup>   | T <sup>(3)</sup>              |

| Physical properties and conformance to MICD Acceptance level | No Test | No Test            | Ţ(3)                          |

| Shock                                                        | No Test | T <sup>(2)</sup>   | No Test                       |

| Packing/Shipping                                             | P       | P                  | P                             |

If FCU:

(0) with PB

(1) PSU EM assembled with the FCU box

(2) PSU STM assembled with the FCU box and PB is used

(3) PSU FM is assembled with the FCU box

### **Sub unit test matrix (SCU or MCU)**

| Test / Model            | STM | QM1                                     | QM2 | FM        |

|-------------------------|-----|-----------------------------------------|-----|-----------|

| Inspection              | NA  | A                                       | A   | A         |

| Electrical tests        | NA  | T                                       | Т   | T         |

| Functional tests        | NA  | T                                       | T   | T         |

| Performance tests       | NA  | T                                       | Т   | T         |

| Vibration tests         | NA  | NA                                      | NA  | NA        |

| Qualification level     |     |                                         |     |           |

| Acceptance level        |     |                                         |     |           |

| Thermal balance tests   | NA  | NA                                      | NA  | NA        |

| Thermal tests           | NA  | NA                                      | NA  | NA        |

| Qualification level     |     |                                         |     |           |

| Acceptance level        |     |                                         |     |           |

| EMI/EMC tests           | NA  | NA                                      | NA  | NA        |

| Qualification level     |     |                                         |     |           |

| Acceptance level        |     |                                         |     |           |

| Physical properties and | NA  | NA                                      | NA  | NA        |

| conformance to MICD     | 0   | *************************************** | 01  | 420000000 |

| Shock                   | NA  | NA                                      | NA  | NA        |

SCU QM1 tests are performed by the SEDI.

For QM2 and FM models, tests are performed using the means and procedures delivered by the SEDI.

MCU performance tests are part of those realized by the LAM. Tests concern the inspection at delivery of the MCU in its FCU like box.

### **Integrated DCU / FCU test matrix**

| Test / Model                                               | QM1 | QM2              | FM               |

|------------------------------------------------------------|-----|------------------|------------------|

| Integration / verification                                 | A   | A                | A <sup>(3)</sup> |

| Electrical tests                                           | T   | T                | T <sup>(3)</sup> |

| Functional tests                                           | T   | $T^{(0)}$        | T <sup>(3)</sup> |

| Performance tests                                          | NA  | T <sup>(1)</sup> | T <sup>(3)</sup> |

| Vibration tests<br>Qualification level<br>Acceptance level | NA  | No Test          | No Test          |

| Shock tests                                                | NA  | No Test          | No Test          |

| Thermal balance tests                                      | NA  | No Test          | No Test          |

| Thermal vacuum tests Qualification level Acceptance level  | NA  | No Test          | No Test          |

| EMI/EMC tests Qualification level Acceptance level         | NA  | No Test          | No Test          |

| Physical properties and conformance to MICD                | NA  | NA               | NA               |

(0) with the PB

the PSU EM is assembled with the FCU box

(3) the PSU FM is assembled with the FCU box

# Tests with JPL Cryostat

# DRCU Programme Review 4th Feb 2003

### Eric Sawyer

### **Topics**

- DDR documentation

- Instrument development plan

- Instrument schedule

- Instrument status

#### **Documentation**

- Review process has been going for some time

- Documents reviewed, comments sent 30 Sept 02

- Response to comments received 2 Dec 02

- Latest documents issued 18 Feb 03

- Review of documents ongoing, but almost complete

- Most comments incorporated, some minor iteration required. Document standard very good

### SPIRE development plan.

STM – No electronics, not deliverable to S/C

AVM – No DRCU, functions are within the FPU simulator. Deliverable to S/C.

CQM – DRCU required, QM 1. Deliverable.

PFM - DRCU required, QM 2 to start then replaced by FM

FS - TBD

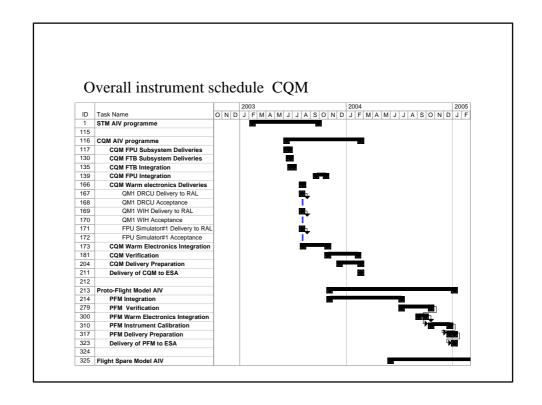

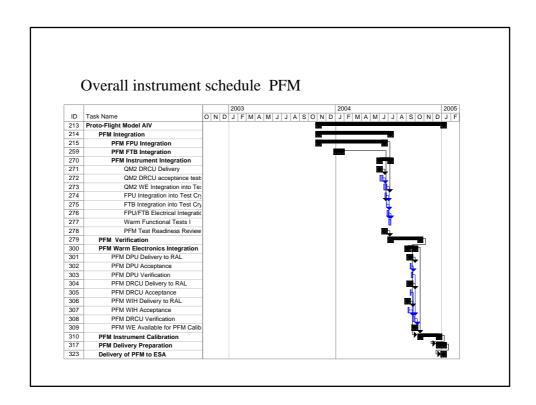

### **Schedule summary**

- QM1 –July 03 Consistent with SPIRE schedule provided a delivery to ESA of Feb 04 is acceptable. If an earlier delivery is required then QM1 is not ok.

- QM2 July 04(TBC) Required in May 04

- PFM Feb 05 (TBC) Required in September 04

### **Current instrument status**

- STM structure manufactured, AIT to start this month

- STM cooler and BSM at RAL, cold vibration test carried out.

- STM/CQM mirrors available

- STM detectors ready to send.

- AVM DPU complete, in test.

# **SPIRE DRCU Review**

CEA-Saclay – March 4, 2003

# **DRCU Development and Procurement plan**

J-L.Auguères

### CEA Warm Electronics delivery commitments:

### Detector Readout and Control Unit (DRCU)

The DRCU encompasses 3 sub-units and a Power Supply (PSU):

Detector Control Unit (DCU)

Subsystem Control Unit (SCU)

Mechanism Control Unit (MCU)

developed by CEA/SEDI

developed by CNRS/LAM

The DRCU comprises 3 boxes: mechanical design by CEA/SAp

- DCU Box.

- FCU (Focal plane Control Unit) containing the MCU and the SCU;

- PSU box which is bolted under the FCU box.

### – Warm Interconnect Harnesses:

- Harnesses between the DPU and the 3 DRCU sub-units.

- Power harness between the PSU and the DCU.

- Focal Plane simulator.

developed by CEA/SIS

### SPIRE Products:

### – DRCU

- DCU

- FCU

- MCU

- SCU

- PSU

- WIHs

### - EGSE

- LTU (Local Test Unit)

- FPU Simulator

- Power Bench

- Test harnesses

### DRCU Model definition:

- STM (commonalities with PACS WE boxes)

- EM

- DCU EM realised and test in collaboration with JPL/Caltech

- QM1

- Form and fit boards in "light" boxes

- Commercial parts

- No redundancy

- QM2

- Comprehensive Flight type model.

- Intended to undergo environmental tests at Qualification level.

- FM

- FS

- Spare units

### CEA deliveries versus ESA models:

- AVM None

- CQM QM1

- FM/FS FM/FS

### DRCU model features

|      |                 |               |            | FCU        |                 |            |          |

|------|-----------------|---------------|------------|------------|-----------------|------------|----------|

| DRCU | Mechanics       | DCU           | MCU        | SCU        | PSU             | Part Grade | Perform. |

| ВВ   | N/A             | Yes           | Yes        | Yes        | -               | Standard   | NNP      |

| STM  |                 | Yes           |            |            |                 |            | N/A      |

| QM1  | Simplified<br>- | EEq(*)<br>NCR | EEq<br>NCR | EEq<br>NCR | PB<br>NCR       | EEq        | NNP      |

| QM2  | F<br>-          | FEq<br>CR     | FEq<br>CR  | FEq<br>CR  | STM,EM,PB<br>CR | FEq        | NNP      |

| FM   | F ·             | F<br>CR       | F<br>CR    | F<br>CR    | F               | F          | NoP      |

| FS   | F<br>?          | F<br>?        | F<br>?     | F<br>?     | F<br>?          | F          | NoP      |

Ext : External (Power Supply only)

EEq : Electrically Equivalent

FEq : Flight Equivalent (any grade but nominal size, consumption and performances)

F : Flight

NCR: Cold Redundancy Not implemented

CR : Cold Redundancy implemented

DeP: Degraded Performance acceptable

NNP: Near Nominal Performance

NoP: Nominal Performance

(\*) : The number of readout channels implemented shall at least correspond to the number of detectors of the instrument CQM (photometer and spectrometer).

### DRCU Models detailed content:

| S-Syst (MI)      | S-Syst (N2) | S-Sys (N3) | Part n° | STM  | EM        | QVI   | QV2      | FM   | FS    |

|------------------|-------------|------------|---------|------|-----------|-------|----------|------|-------|

|                  |             |            |         |      |           |       |          |      |       |

| DOU .            |             |            |         |      |           |       |          |      |       |

| <u> </u>         | DAQHF       |            |         | 2dum | 1         | 1     | 2        | 2    | 1     |

|                  | BIAS        |            |         | 2dum | 1         | 1     | 2        | 2    | 1     |

|                  | LIATC       |            |         | 1dum | 0         | 0     | 1        | 1    | 1     |

|                  | LIAS        |            |         | 3dum | 3         | 3     | 3        | 3    | 1     |

|                  | LIAP        |            |         | 8dum | 2         | 2     | 8        | 8    | 2     |

|                  | BP-DOU      |            |         | 1dum | 1 (QM1)   | 1     | 1        | 1    | 1     |

|                  | DOUBox      |            |         | 1    | 1 (QVII)  | Light | 1        | 1    | ı     |

| FOJ              |             |            |         | ı ı  | I (GIVII) | цуп   | !        | ļ ļ  |       |

| Ι ω              | san         |            |         |      |           |       |          |      |       |

|                  |             | CCHK+IF    |         | _    | _         | 1     | 2        | 2    | 1     |

|                  |             | Temp+Heat  |         | _    | _         | 1     | 2        | 2    | 1     |

|                  |             | BP-SCU     |         | _    | _         | 1?    | 1        | 1    | 1     |

|                  | MOU         |            |         | _    | _         | 1     | 1        | 1    | ?     |

|                  | SCUBox      |            |         | _    | _         | Light | <u> </u> | _    | _     |

|                  | FOUBox      |            |         | _    | _         | Light | 1        | 1    | _     |

| PSU              | 1 33 23 (   |            |         | 1    | Lab.      | PB    | PB/EM    | PB/1 | Board |

| Flight Harnesses |             |            |         |      |           |       | 1001     |      | Doard |

|                  | DROUDPU     |            |         | _    | _         | 1     | 2        | 2    | _     |

|                  | PSUDOU      |            |         | _    | _         | 1     | 2        | 2    | _     |

|                  | PSUFCU      |            |         | -    | -         | 1     | 2        | 2    | -     |

|                  | 30.00       | PSUSCU     |         | -    | -         | 1     | 2        | 2    | -     |

|                  |             | PSUMOU     |         | -    | -         | 1     | 2        | 2    | -     |

### Procurement Plan:

#### Boxes and Boards

· All models:

Design : in house

Detailed drawings : industry

Realisation : industry

Mechanical simulations : industry

Thermal simulations : in house

Environmental tests : industry

### – Electronics parts:

Test equipments

QM1

Self Procurement

Self Procurement

QM2, FM, FS

– OP400 (custom packaging) : Self Procurement

- Others : CPPA

## Procurement Plan (cont.):

– Harnesses:

Test harnesses

Specification : in houseFabrication files : industry

Parts (connectors, wires) : Self Procurement

Realisation : industry

WIH (DPU to DCU, DPU to FCU, DCU to FCU power harness)

Specification : in house (+ Alcatel inputs)

Fabrication files : in house

Parts (connectors, wires) : Self Procurement

Realisation : industryEnvironmental tests : industry

- EGSEs:

- FP Simulators (1 deliverable)

Specification : in house

Design : in house

Electronics Board realisation : industry

Labyiew S/W : in house

Standard parts (chassis, P.Sup...) : commercial procurement

Integration & tests : in house

LTUs (Local Test Unit).

Specifications (H/W & S/W) : in house

Overall Design : in house

H/W detailed design & realisation : industry

S/W : in house

H/W – S/W Integration & tests : in house

Power Benches.

Specification : in house

Overall design : in house

Detailed design & realisation : industry

Integration and test : industry

- Procurement Plan (cont.):

- DRCU QM1:

- DCU, SCU Boards:

Design · in house PCB routing : in house Wiring : industry Flectrical tests : in house Functional Tests : in house Performance Validation : in house DCU, SCU Integration & Test : in house FCU Integration & Tests : in house

### - DRCU QM2:

• DCU, SCU Boards:

PCB routing : in house

Wiring : industry

Electrical tests : industry

Functional Tests : in house

Performance checking : in house

DCU, SCU Integration & Test : In house

FCU Integration & Tests : in house

• Environmental tests : industry + CEA

### **DRCU Development and Procurement – Procurement Plan**

– DRCU FM/FS:

DCU, SCU Boards:

PCB routing : in house

Wiring : industry

Electrical Tests : industry

Functional Tests : industry

Performance checking : industry

• DCU, SCU Integration & Test : TBD

• FCU Integration & Tests : in house

• Environmental tests : industry + CEA

### Development Status:

- DCU (Detector Control Unit)

- QM1:

- Box and back-plane available.

- Boards:

- » 1 DAQ+IF + 1 BIAS, 1 LIA fabricated, functions and performances checked.

- » 4 LIA under fabrication.

- Pre-integration started:

- » Box & Back-plane: OK

- » Functional test OK

- » Performance test ongoing

- FCU (Focal plane Control Unit)

- QM1:

- Box available

- SCU (Sub-system Control Unit)

cf SCU presentation

- MCU (Mechanism Control Unit): cf MCU presentation by LAM

### Development Status (cont.):

#### – PSU:

- Specification available.

- Call for tender process started.

- FM fab. Time 14 months (6 months to be added for contract sign off).

#### Boxes:

- I/F (external & internal) and design OK.

- QM1 "light" boxes (DCU + FCU) available.

- STM: Box (QM) and Mec. & Thermal mock-up boards available.

- QM boxes:

- DCU available (STM box)

- FCU ready for manufacturing.

### Development Status (cont.):

#### EGSEs

- Local Test Unit:

- Specification & Architecture OK.

- H/W: procurements OK fabrication ongoing.

- S/W: under development.

- 2 units will be manufactured:

- » Availability of the 1st unit: March 03

- FP Simulator:

- Spec. Architecture & User manual available.

- First unit: available.

- Second unit: fabrication started.

- Power Benches:

- Specifications available.

- 3 units will be manufactured

- » 1st unit available in April 03

## Development Status (cont.):

#### – AIV:

- AIV plan available.

- AIV detailed plan and procedures under development.

#### – Harnesses:

- · Connector procurement OK.

- Test harness specification ongoing.

- WIH

## – PA/QA:

- Internal review procedure set up.

- Doc. List and EIDP definition OK.

- Non conformity management procedures available.

- DML and DPL available.

## Documentation Status:

#### – Review documentation:

- See the CEA document list.

- These documents have been submitted to internal reviewing process.

- Next issues submitted to internal Configuration Control.

## – Documentation management:

- Configuration control procedures available.

- Internal documentation database available.

- Internal acces via intranet.

## **DRCU Documentation Status**

| Management plan for the Herschel project.      | SAp-FIRST-JLA-0038-01   | 4.0 23/01/2003 |

|------------------------------------------------|-------------------------|----------------|

| DRCU & WIH Development Plan                    | SAp-SPIRE-JLA-0047-01   | 4.0 29/01/2003 |

| SPIRE product tree                             | SAp-SPIRE-DR-0094-03    | 1.0 21/01/2003 |

| WBS Herschel                                   | SAP-FIRST-DR-0043-01    | 2.1 30/11/2001 |

| WBS SPIRE                                      | SAP-FIRST-DR-0045-01    | 2.1 30/11/2001 |

| SPIRE DRCU QM1master schedule                  | SAp-FIRST-DR-105-01     | 1 18/02/2003   |

| DRCU Specifications document                   | SAp-SPIRE-Cca-0025-00   | 1.0 14/02/2003 |

| Division opcomodations decarrient              | (SPIRE-SAP-PRJ-000461)  | 1.0 14/02/2000 |

|                                                | (SFIRE-SAF-FR0-000401)  |                |

| DRCU ICD                                       | SAp-SPIRE-Cca-0075-02   | 1.0 14/02/2003 |

|                                                | (SPIRE-SAP-PRJ-000451)  |                |

|                                                | r r                     |                |

| DRCU DPU ICD                                   | SAp-SPIRE-Cca-0076-02   | 1.0 14/02/2003 |

|                                                | (SPIRE-SAP-PRJ-001364)  |                |

|                                                | ſ                       |                |

| DCU design document                            | SAp-SPIRE-FP-0063-02    | 0.3 18/02/2003 |

| Test plan DAQ IF                               | SAp-SPIRE-FP-0067-02    | 0.1 draft      |

| Test plan BIAS                                 | SAp-SPIRE-FP-0066-02    | 0.1 draft      |

| Test plan LIA P                                | SAp-SPIRE-FP-0064-02    | 0.1 draft      |

| Test plan LIA S                                | SAp-SPIRE-FP-0065-02    | 0.1 draft      |

| SPIRE test configuration                       | SAp-SPIRE-LD-0015-01    | 3.0 08/2001    |

| FPU simulator specs for DCU / SCU test         | SIG-SPIRE-PdA-0030-01   | 03 14/02/2003  |

| SPIRE LTU specifications                       | SAp-SPIRE-FD-0071-02    | 1.0 22/04/2002 |

| DRCU AIV Plan                                  | SAp-SPIRE-HT-0082-02    | 2.0 03/02/2003 |

| DRCU EM/QM1 preliminary test plan              | SAp-SPIRE-HT-0088-02    | 0.1 14/02/2003 |

| SCU design document                            | SEDI-SCU-MM-2002-1      | 0.7 17/02/2003 |

| PSU SPIRE specification                        | SAp-SPIRE-DS-012-02     | 1.1 11/12/2002 |

| PA Plan                                        | SAP-GERES-Flo-436-00    | 1.0 07/11/2000 |

| DPL                                            | SAp-SPIRE-NC-0061-02    | 1.0 13/02/2003 |

| DML                                            | SAp-SPIRE-NC-0060-02    | 1.0 13/02/2003 |

| DMPL                                           | SAp-SPIRE-NC-0100-02    | 1.0 13/02/2003 |

| DCL                                            | SAp-SPIRE-VM-0098-02    | 14 10/02/2003  |

| Synthesis note about DRCU FMEA and reliability | SAp-SPIRE-JF-0099-03    | 0.1 10/02/2003 |

| WCA (and derating??)                           | will be performed later |                |

|                                                |                         |                |

# **DRCU Development and Procurement – Documentation**

# ADP (as per H/W ADP content (RAL))

| Documents                                         | QM1        | FM         | Comments                                                                                                                          | Doc. status<br>QM1                         |

|---------------------------------------------------|------------|------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| shipping documents                                | yes        | yes        |                                                                                                                                   |                                            |

| procedure for transport handling and installation | yes        | yes        |                                                                                                                                   |                                            |

| C of C/Delivery Review Board MOM Al-Lists         | yes        | yes        |                                                                                                                                   |                                            |

| Qualification status list /test matrix            | yes        | yes        | Inluded in DRB minutes/report                                                                                                     |                                            |

| Top level draw ings (inc. familly tree)           | yes        | yes        |                                                                                                                                   |                                            |

| Interface drawings                                | yes        | yes        |                                                                                                                                   | SPIR-MX-5101 000<br>SPIR-MX-5201 000       |

| Functional diagrams                               | yes        | yes        | cut and paste from DRCU subsystem specs                                                                                           |                                            |

| Electrical circuits diagrams                      | yes        | yes        | full diagrams are kept in our premices; i/f electrical diagrams are included in ICD (SAp-SPIR-CCa-075-02 and SAp-SPIR-CCa-076-02) | SAp-SPIR-CCa-075-02<br>SAp-SPIR-CCa-076-02 |

| As Built Configuration Statis List                | yes        | yes        |                                                                                                                                   |                                            |

| Serialised components list                        | n/a        | yes        |                                                                                                                                   |                                            |

| List of waivers                                   | yes        | yes        | To be included in ABCL                                                                                                            |                                            |

| Copies of waivers                                 | yes        | yes        | To be included in ABCL                                                                                                            |                                            |

| Operational manual                                | yes        | yes        |                                                                                                                                   |                                            |

| Historical record                                 | yes        | yes        |                                                                                                                                   |                                            |

| Logbook/ Diary of events                          | yes        | yes        |                                                                                                                                   |                                            |

| Operating time/Cycle record                       | N/A        | N/A        |                                                                                                                                   |                                            |

| Connector mating record                           | N/A        | yes        | included in logbook / Diary of events                                                                                             |                                            |

| Age sensitive Items record                        | N/A        | N/A        |                                                                                                                                   |                                            |

| Pressure Vessel History / test record             | N/A        | N/A        |                                                                                                                                   |                                            |

| Calibration data record                           | N/A        | N/A        |                                                                                                                                   |                                            |

| Temporary installation record                     | yes        | yes        | included in logbook / Diary of events                                                                                             |                                            |

| Open w ork / Deffered w ork / Open tests          | if applies | if applies |                                                                                                                                   |                                            |

| List of non-conformance reports                   | yes        | yes        | included in ABCL (if any)                                                                                                         |                                            |

| Test reports                                      | yes        | yes        | list of test reports inclued in EIDP to be determined                                                                             |                                            |

| Proof load certificate                            | N/A        | N/A        |                                                                                                                                   |                                            |

| Reference list of low er level ADP's              | yes        | yes        | QM1: MCU only; FM: MCU and PSU                                                                                                    |                                            |

| Cleanliness statement                             | yes        | yes        |                                                                                                                                   |                                            |

| Compliance matrix                                 | yes        | yes        |                                                                                                                                   |                                            |

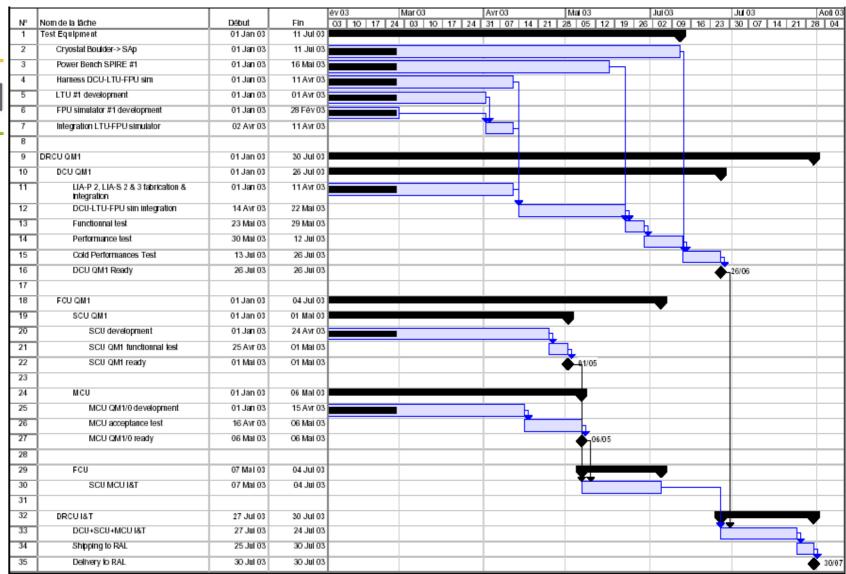

## **DRCU Development and Procurement - QM1 Schedule**

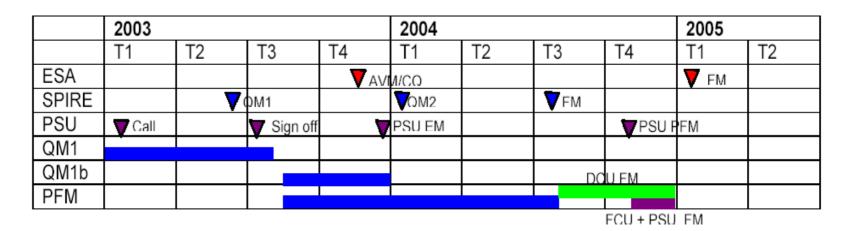

#### Scenario 1:

- The original development plan is kept: QM1, QM2, FM

- Schedule risks on QM1 due to:

- 1. Cryogenic test with the JPL test Bolometer.

- 2. Activities within the holidays period.

- Limited feedback for QM2: no test with the actual JPL CQM bolometers.

|       | 2003          |    |          |             | 2004         |    |             |          | 2005 |    |

|-------|---------------|----|----------|-------------|--------------|----|-------------|----------|------|----|

|       | T1            | T2 | T3       | T4          | T1           | T2 | T3          | T4       | T1   | T2 |

| ESA   |               |    |          | VA <b>▼</b> | N/CO         |    |             |          | ▼ FM |    |

| SPIRE |               | V  | DM1      |             | <b>V</b> OM2 |    | <b>V</b> FM |          |      |    |

| PSU   | <b>▼</b> Call |    | Sign off | <b>_</b>    | PSU EM       |    |             | ▼PSU F   | FM   |    |

| QM1   | •             |    |          | •           |              |    |             | <u>-</u> |      |    |

| QM2   |               |    |          |             |              |    |             |          |      |    |

| FM    |               |    |          |             |              |    |             |          |      |    |

- The QM2 development takes one year (give or take):

- 1. QM2 board layouts have to be revised to take into account: the QM1 feedback and the use of flight component packaging.

- 2. The test with the PSU EM.

- 3. The environment testing at Qualification level requiring margins.

- DRCU FM available by end February 2005.

## Scenario 1 (cont.)

#### Pros:

- 1. The full development is carried out minimising the risk.

- 2. The PSU EM can be tested with a flight representative model.

- 3. The PSU FM power supply can be integrated and tested with the full DRCU FM prior to its delivery.

#### Cons:

1. Late availability of the DRCU FM.

#### Conclusion:

- 1. This scenario is the nominal one and the optimal one (as it minimises the risk).

- The schedule issue could not be an issue as it is likely that other subsystems (WE or focal planes) will have comparable schedule shift (if not worse).

#### Scenario 2:

- The QM2 is cancelled and a QM1b and a PFM are built consecutively:

- After the delivery of the QM1, a second QM1 (QM1b) is built.

- The QM1b is identical to the QM1 (light box, Standard components, no redundancies) but all detector readout and control channels are implemented.

- The QM1b is intended:

- 1. To test as far as possible the PSU (EM) compatibility.

- 2. To be used with the Instrument PFM.

|       | 2003          |    |          |              | 2004   |    |             |        | 2005 |    |

|-------|---------------|----|----------|--------------|--------|----|-------------|--------|------|----|

|       | T1            | T2 | T3       | T4           | T1     | T2 | T3          | T4     | T1   | T2 |

| ESA   |               |    |          | <b>V</b> AVI | M/CO   |    |             |        | ▼ FM |    |

| SPIRE |               | V  | 0M1      |              | VOM2   |    | <b>▼</b> FM |        |      |    |

| PSU   | <b>▼</b> Call |    | Sign off | <b>\</b>     | PSU EM |    |             | ▼PSU F | FM   |    |

| QM1   | •             |    |          | •            |        |    |             | •      |      |    |

| QM1b  |               |    |          |              |        |    |             |        |      |    |

| PFM   |               |    |          |              |        |    |             |        |      |    |

DRCU FM available by the end of 2004.

#### • Pros:

- 1. Provides a good feedback between the QM1 and the PFM.

- 2. Provides electronics to drive the PFM Focal Plane.

- 3. The PFM delivery date is "optimised" against the PSU PFM availability date.

#### Cons:

- 1. PFM development: high risk in case of failure at any level and especially during the environment test.

- 2. The Flight Model has to undergo the Qualification level (instead of acceptance).

- 3. There is no model to validate the electrical compatibility of the PSU with the PSU EM.

#### Conclusions:

- This scenario has two major drawbacks:

- 1. The DRCU development not in line with the PSU development.

- 2. High risks are taken due to the PFM policy.

- Given the schedule shifting risks, the advantage to get the PFM earlier than in the case of the scenario 1 is not obvious.

## **DRCU Development and Procurement – Model sequence scenarios**

#### Scenario 3:

- The QM2 is cancelled and a QM1b and a PFM are built in parallel.

- The QM1b and its objectives are the same as in the scenario 2.

- In this case, the DRCU FM powered by a power bench could be available by October 2004 but the PSU FM has to be integrated later when available.

- DRCU FM available by the end of 2004.

## **DRCU Development and Procurement – Model sequence scenarios**

#### – Pros:

- 1. Provides electronics to drive the PFM Focal Plane.

- 2. The PFM delivery date is "optimised" against the PSU PFM availability date.

- 3. The DCU FM can be used with the Focal Plane PFM.

- 4. The PSU EM can be tested with a flight representative model.

#### - Cons:

- 1. PFM development: high risk in case of failure at any level and especially during the environment test.

- 2. The Flight Model has to undergo the Qualification level (instead of acceptance).

- 3. Two models (QM1b and PFM) have to be built in parallel (resource issue).

#### – Conclusion:

- This scenario has two major drawbacks:

- 1. High risks are taken due to the PFM policy.

- 2. High workload peak when the QM1b and the PFM development are in parallel.

- Given the schedule shifting risks, the advantage to get the PFM earlier than in the case of the scenario 1 is not obvious.

Herschel-SPIRE : DRCU Programme Review

CEA-SAp

March 4, 2003

# **Mechanisms Control Unit**

## The dates

#### D. Pouliquen

#### Laboratoire d'Astrophysique de Marseille

MCU

D.Pouliquen, L.A.M.

Slide 1

Herschel-SPIRE : DRCU Programme Review

CEA-SAD

March 4, 2003

#### MCU QM0 and QM1

- > QM0 : for communication and LTU tests

- Design + routing+ tests at LAM + manufacture in industry)

- New model introduced for planning reasons

- Form & fit, electrical, command interface & flight functions nearly Ok

- ALTERA FPGA including CEA DAPNIA Communication VHDL issue 0.4

- · Commercial components, no redundancy

- Not suitable for mechanisms control

- Delivered with mechanisms simulator and cables

- Delivery date April 2003

- > QM1 : for CQM tests

- Design + routing + tests at LAM + manufacture in industry

- Tested with the CQM mechanisms => QM0 modified for mechanism control capability => flight functions Ok at time of delivery

- Delivery date = end of July 2003

MCU

D.Pouliquen, L.A.M.

Slide

Herschel-SPIRE: DRCU Programme Review

CEA-SAp

March 4, 2003

#### MCU QM2

- Design = QM1 (LAM) as delivered to CEA

- Design does not include modifications needed after SPIRE CQM tests

- Subcontracted in the industry (studies, routing, manufacture, electrical and environment tests)

- End of studies = 15 Aug 2003 (t0 + 5 months)

Studies includes mechanical and thermal studies as the subcontractor is responsible for the MCU thermal and mechanical behaviour.

- QM2 manufacture and tests from 15 Aug 2003 to 31 Jan 2004 (duration : 5.5 months)

- Tests include vibrations, thermal tests and performance tests with simulators all made at LAM

- QM2 delivery to CEA => end Feb 2004 (t0 + 11.5 months)

If need for QM1 design modification arises during CQM programme, the QM2 will not have them. This raises a question (no answer yet) on the ability of QM2 to pilot the FPU mechanisms inside the FPU.

MCU

D.Pouliquen, L.A.M.

Slide 3

Herschel-SPIRE : DRCU Programme Review

CEA-SAp

March 4, 2003

#### MCU FM & FS

- Design = QM1 + mechanical and thermal studies made and validated at LAM with the QM2

- Design does not include modifications needed after SPIRE CQM nor after FCU QM2 tests (tests made at FCU level, after beginning of FM manufacture i.e. vibr, thermal and EMI)

- If no electrical modification w.r.t. QM1 as delivered to CEA,

- ➤FM manufacture and tests from 1st Feb 2004 (end of QM2 manufacture + no modifs) to 1st Sep 2004 (duration : 7 months)

- ➤ FM delivery to CEA => 31 Oct 2004 (end of QM2 at LAM + 9 months): will not have seen the PFM mechanisms before delivery

- ➤FS (=FM) availability at LAM = 1st Nov 2004 (end of FM + 2 months) => available for the project 1st Jan 2005

MCU

D.Pouliquen, L.A.M.

Slide

# **SPIRE DRCU Review**

CEA-Saclay – March 4, 2003

**Management & Staff**

J-L.Auguères

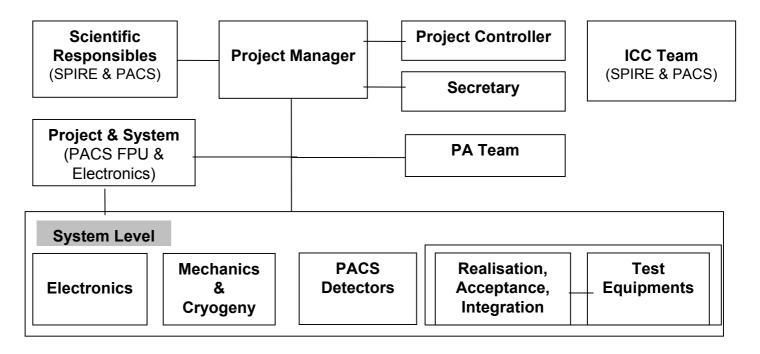

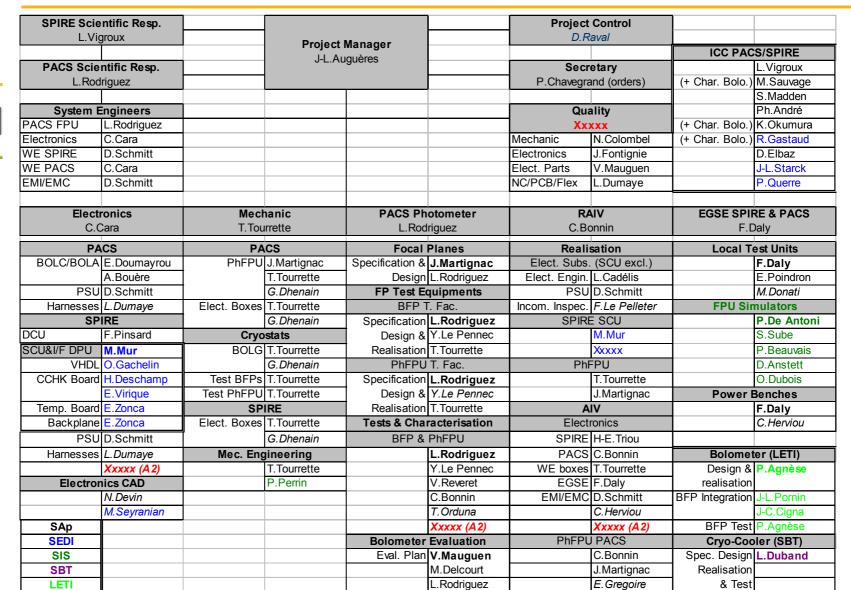

## Managerial organisation:

- Two projects (SPIRE & PACS), one Herschel team.

- Main reasons:

- Resource management flexibility.

- Common Development.

## Herschel Teams:

## Project & System Team

- Members: Scientific Responsibles, the Project Manager, the PA Responsible and Team key persons.

- Check system consistency of the design and development against the system requirements.

- Discuss, sort out technical and programmatic issues, make any decisions at system level.

#### Electronics Team

Design and development of the Electronics sub-systems.

## Mechanic and Cryogeny Team

- Design and development of the PACS and SPIRE electronics boxes.

- Development and setting up and maintenance of the cryogenic test facilities.

- Design and development of the PACS Photometer Focal Plane mechanics and mounting tools.

## Herschel Teams (cont.):

#### PACS detector team:

• In charge of the overall design, the development, the test and the characterisation of the PACS Photometer Focal Plane.

## Test Equipment, Realisation and AIV team:

- Development and commissioning of the electronics ground test equipment.

- Realisation and integration of the qualification and Flight models.

- Qualification, Validation and delivery.

#### – Product assurance team:

- Writing and maintenance of the PA documents (PAPs, method and procedures, Parts Lists,...)