# Herschel SPIRE

| Document    | SEDI /SCU/MM/2002-1 | V 0.6          | Published 30/06/2002   |

|-------------|---------------------|----------------|------------------------|

| Edited by   | Michel MUR          | 01 69 08 14 67 | michel.mur@cea.fr      |

| Chaokad by  | Hervé DESCHAMPS     | 01 69 08 61 68 | hervé.deschamps@cea.fr |

| Checked by  | Eric DOUMAYROU      | 01 69 08 25 98 | eric.doumayrou@cea.fr  |

| Reviewed by | Jean FONTIGNIE      | 01 69 08 14 19 | jean.fontignie@cea.fr  |

# Control Unit (SCU)

This document describes the SCU, one of the 3 sub-units of the Herschel/SPIRE/DRCU electronic subsystem.

# TABLE OF CONTENTS

#### **FIGURES**

Ш

| TABLES   |                    |       |                                   | IV            |

|----------|--------------------|-------|-----------------------------------|---------------|

|          |                    |       |                                   | _             |

| <u>1</u> | INTRODUCTION       |       |                                   | 5             |

|          | 1.1                | APPLI | CABLE DOCUMENTS                   | 5             |

|          |                    | 1.1.1 | SPECIFICATION DOCUMENTS           | 5             |

|          |                    | 1.1.2 |                                   | 5             |

|          |                    | 1.1.3 |                                   | 5             |

|          | 1.2                | OVER  |                                   | 5<br><b>5</b> |

|          |                    | 1.2.1 | ACQUISITION AND CONTROL FUNCTIONS |               |

|          |                    | 1.2.2 |                                   |               |

|          |                    | 1.2.3 | DPU INTERFACE FUNCTIONS           | 6             |

| <u>2</u> | ARCHITECTURE       |       |                                   | 7             |

| -        | <u></u>            |       |                                   |               |

|          | 2.1                | BLOCH | K DIAGRAM                         | 7             |

|          | 2.2                | BEHA  | /IOUR                             | 8             |

|          |                    | 2.2.1 | DATA FRAME SEQUENCE               | 8             |

|          |                    | 2.2.2 | SUBSYSTEM PARAMETER ACCESS        | 8             |

| <u>3</u> | DIGITAL FUNCTIONS  |       |                                   | 9             |

|          | 3.1                | GENE  | RIC DPU INTERFACE                 | 9             |

|          | 3.2                |       | SUBSYSTEM LOGIC                   | 9             |

| <u>4</u> | ANALOGUE FUNCTIONS |       |                                   | 11            |

|          | 4.1                | COOLI | ER HIGH POWER HEATER (HEATERH)    | 11            |

|          |                    |       | SPECIFICATION                     | 11            |

|          |                    |       | GENERAL DESCRIPTION               | 11            |

|          |                    |       | SIMULATION                        | 12            |

|          |                    |       | PROTOTYPE TEST RESULTS            | 14            |

|          | 4.2                |       | ER GAS PUMP HEATERS (HEATERL)     | 19            |

|          |                    | 4.2.1 |                                   | 19            |

|          |                    | 4.2.2 |                                   | 19            |

|          |                    | 4.2.3 |                                   | 20            |

|          |                    | 4.2.4 |                                   | 21            |

|          | 4.3                |       | HERMAL STRAP HEATER (HEATERL)     | 24            |

|          |                    | 4.3.1 | SPECIFICATION                     | 24            |

|          |                    | 4.3.2 |                                   | 24            |

24

26

26

|                                                            | 4.4.2 CIRCUIT DESCRIPTION                                                                                                                                         |             |

|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|                                                            | 4.4.2 CIRCUIT DESCRIPTION<br>4.4.3 SIMULATION                                                                                                                     |             |

|                                                            | 4.4.5 SIMULATION<br>4.4.4 PERFORMANCE REQUIR                                                                                                                      |             |

|                                                            | 4.4.5 PROTOTYPE TEST RESU                                                                                                                                         | -           |

| 4.5                                                        | SUB-K THERMOMETRY : TEMP                                                                                                                                          | -           |

|                                                            | 4.5.1 SPECIFICATION                                                                                                                                               |             |

|                                                            | 4.5.2 DESIGN PRINCIPLE                                                                                                                                            |             |

|                                                            | 4.5.3 BLOCK DIAGRAM                                                                                                                                               |             |

|                                                            | 4.5.4 RESOLUTION                                                                                                                                                  |             |

|                                                            | 4.5.5 PROTOTYPE MEASUREN                                                                                                                                          | IENTS       |

| 4.6                                                        | OTHER THERMOMETRY CHANNE                                                                                                                                          | ELS: TEMPDC |

|                                                            | 4.6.1 SPECIFICATION                                                                                                                                               |             |

|                                                            | 4.6.2 DESIGN PRINCIPLE                                                                                                                                            |             |

|                                                            | 4.6.3 RESOLUTION                                                                                                                                                  |             |

|                                                            | 4.6.4 PROTOTYPE MEASUREN                                                                                                                                          |             |

| 4.7                                                        | ELECTRONICS TEMP. MONITOR                                                                                                                                         | -           |

| 4.8                                                        | POWER SUPPLY MONITOR : PW                                                                                                                                         | /RMON       |

| PHYSICAL IMPLEM                                            | ENTATION                                                                                                                                                          |             |

|                                                            | _                                                                                                                                                                 |             |

| 5.1                                                        | Boards                                                                                                                                                            |             |

|                                                            | BOARDS<br>BACKPLANE                                                                                                                                               |             |

| 5.1                                                        | BOARDS<br>BACKPLANE<br>5.2.1 PSU INTERCONNECTS                                                                                                                    |             |

| 5.1<br>5.2                                                 | BOARDS<br>BACKPLANE<br>5.2.1 PSU INTERCONNECTS<br>5.2.2 BOARD INTERCONNECT                                                                                        | S           |

| 5.1<br>5.2<br>5.3                                          | BOARDS<br>BACKPLANE<br>5.2.1 PSU INTERCONNECTS<br>5.2.2 BOARD INTERCONNECT<br>TEMP BOARD                                                                          | S           |

| 5.1<br>5.2                                                 | BOARDS<br>BACKPLANE<br>5.2.1 PSU INTERCONNECTS<br>5.2.2 BOARD INTERCONNECT                                                                                        | S           |

| 5.1<br>5.2<br>5.3                                          | BOARDS<br>BACKPLANE<br>5.2.1 PSU INTERCONNECTS<br>5.2.2 BOARD INTERCONNECT<br>TEMP BOARD                                                                          | S           |

| 5.1<br>5.2<br>5.3<br>5.4<br><u>OPERATION</u><br>6.1        | BOARDS<br>BACKPLANE<br>5.2.1 PSU INTERCONNECTS<br>5.2.2 BOARD INTERCONNECT<br>TEMP BOARD                                                                          | S           |

| 5.1<br>5.2<br>5.3<br>5.4<br><u>OPERATION</u><br>6.1<br>6.2 | BOARDS<br>BACKPLANE<br>5.2.1 PSU INTERCONNECTS<br>5.2.2 BOARD INTERCONNECTS<br>TEMP BOARD<br>CCHKIF BOARD                                                         | S           |

| 5.1<br>5.2<br>5.3<br>5.4<br><u>OPERATION</u><br>6.1        | BOARDS<br>BACKPLANE<br>5.2.1 PSU INTERCONNECTS<br>5.2.2 BOARD INTERCONNECT<br>TEMP BOARD<br>CCHKIF BOARD<br>WORKING CYCLE                                         | S           |

| 5.1<br>5.2<br>5.3<br>5.4<br><u>OPERATION</u><br>6.1<br>6.2 | BOARDS<br>BACKPLANE<br>5.2.1 PSU INTERCONNECTS<br>5.2.2 BOARD INTERCONNECTS<br>TEMP BOARD<br>CCHKIF BOARD<br>WORKING CYCLE<br>PARAMETER LIST<br>DATA FRAME FORMAT | S           |

<u>5</u>

<u>6</u>

<u>7</u>

| Eleupee   |                                                                          |    |

|-----------|--------------------------------------------------------------------------|----|

| FIGURES   |                                                                          |    |

| FIGURE 1  | SCU BLOCK DIAGRAM                                                        | 7  |

| FIGURE 2  | SCHEMATIC VIEW OF THE HEATERH CIRCUIT                                    | 12 |

| FIGURE 3  | HEATERH SIMULATION : POWER VARIATION                                     | 13 |

| FIGURE 4  | HEATERH SIMULATION : CURRENT VARIATION                                   | 13 |

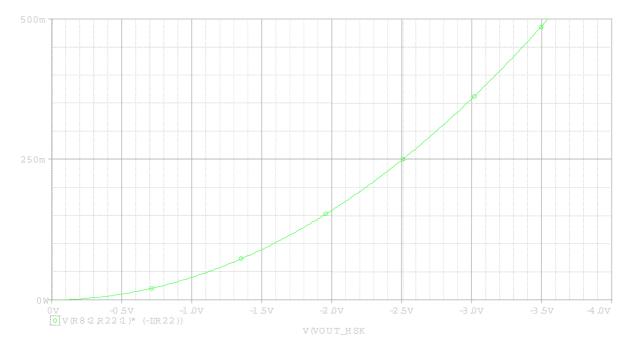

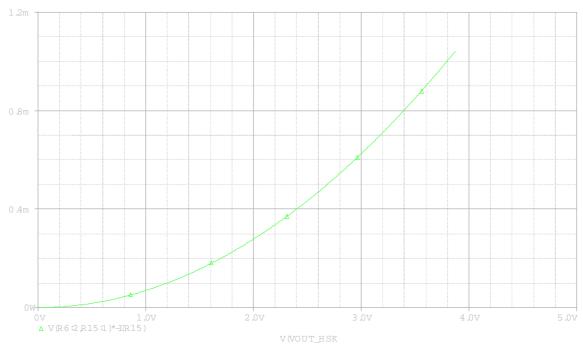

| FIGURE 5  | HEATERH SIMULATION : POWER DISSIPATION VS HSK VOLTAGE                    | 14 |

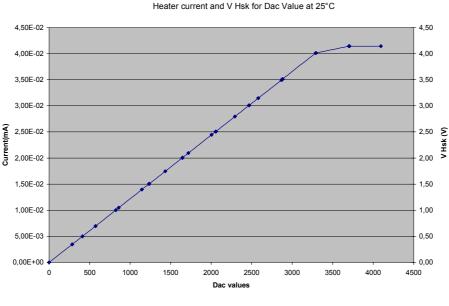

| FIGURE 6  | HEATERH PROTOTYPE : CURRENT VARIATION                                    | 15 |

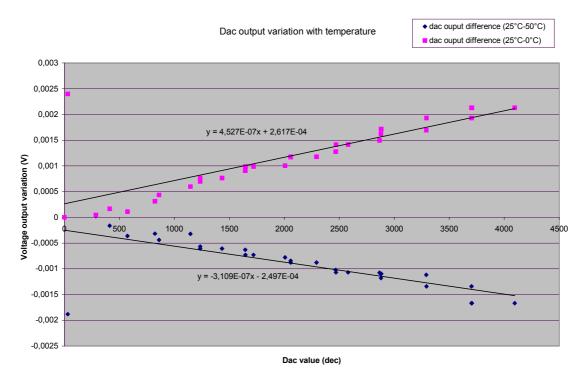

| FIGURE 7  | HEATERH PROTOTYPE : DAC OUTPUT VOLTAGE DEPENDENCE WITH TEMPERATURE       | 16 |

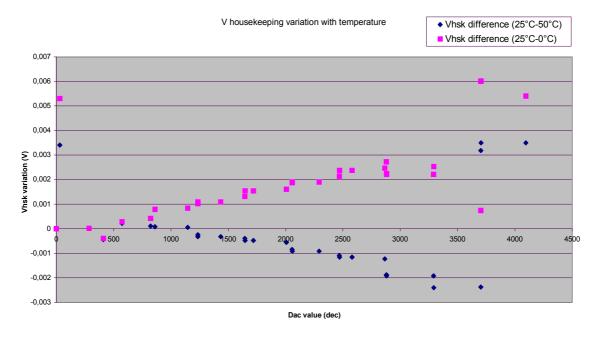

| FIGURE 8  | HEATERH PROTOTYPE : HSK VOLTAGE DEPENDENCE WITH TEMPERATURE              | 17 |

| FIGURE 9  | HEATERH PROTOTYPE : CURRENT DEPENDENCE WITH TEMPERATURE                  | 17 |

| FIGURE 10 | HEATERL CIRCUIT : DESIGN PRINCIPLE                                       | 20 |

| FIGURE 11 | HEATERL SIMULATION : POWER VARIATION                                     | 20 |

| FIGURE 12 | HEATERL SIMULATION : CURRENT VARIATION                                   | 21 |

| FIGURE 13 | HEATERL SIMULATION : POWER DISSIPATION VS HSK VOLTAGE                    | 21 |

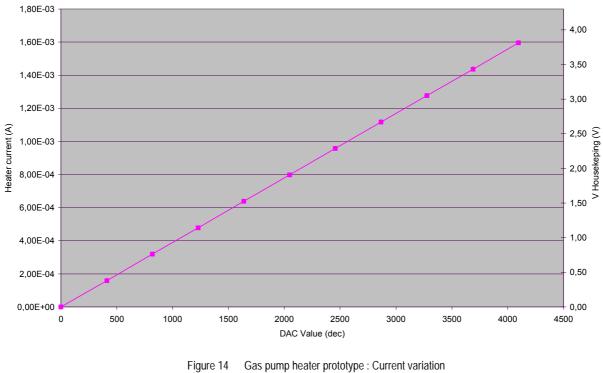

| FIGURE 14 | GAS PUMP HEATER PROTOTYPE : CURRENT VARIATION                            | 22 |

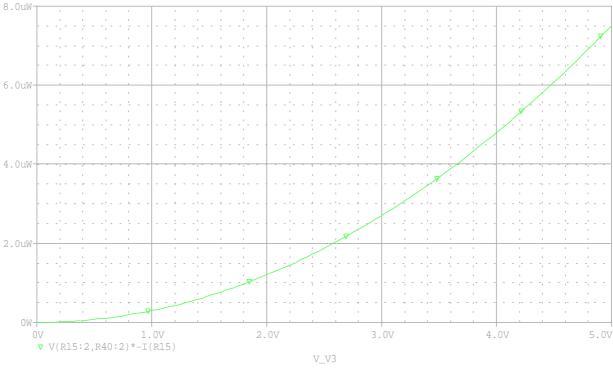

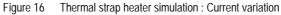

| FIGURE 15 | THERMAL STRAP HEATER SIMULATION : POWER VARIATION                        | 25 |

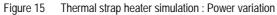

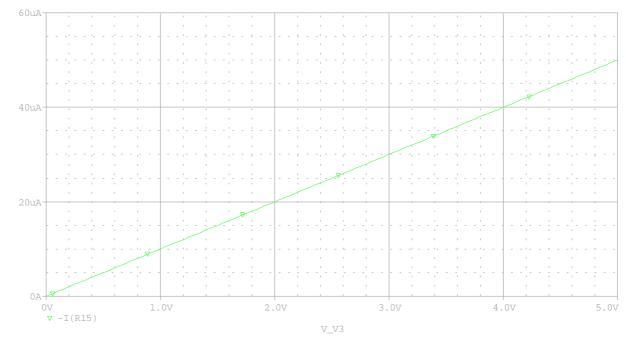

| FIGURE 16 | THERMAL STRAP HEATER SIMULATION : CURRENT VARIATION                      | 25 |

| FIGURE 17 | THERMAL STRAP HEATER SIMULATION : POWER DISSIPATION VS HSK VOLTAGE       | 26 |

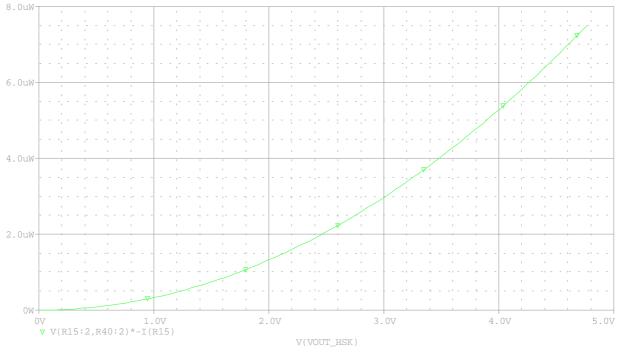

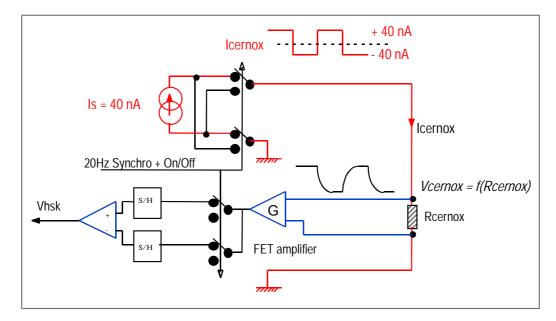

| FIGURE 18 | CALIBRATOR CURRENT SOURCE PRINCIPLE                                      | 28 |

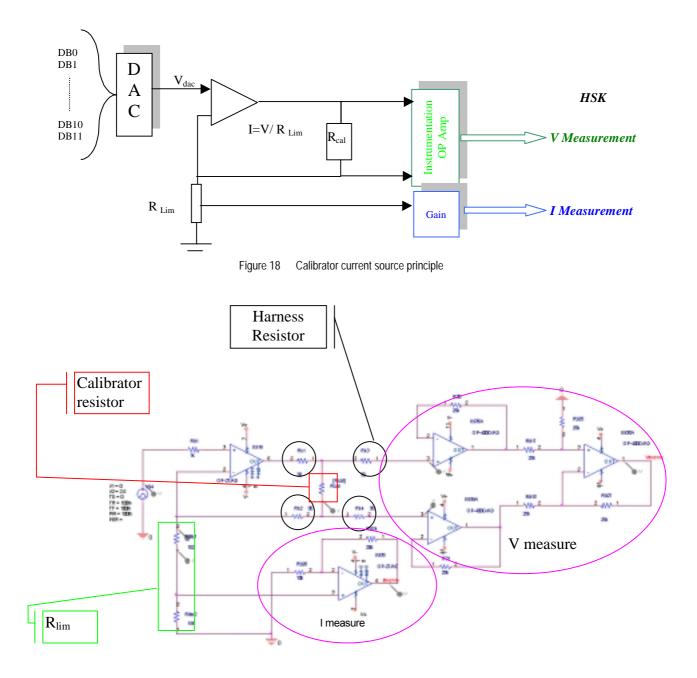

| FIGURE 19 | CALIBRATOR CURRENT SOURCE CIRCUIT                                        | 28 |

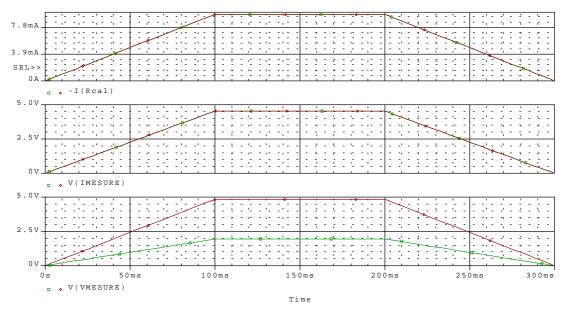

| FIGURE 20 | CALIBRATOR CURRENT SOURCE SIMULATION : CURRENT AND IMEAS/VMEAS VARIATION | 29 |

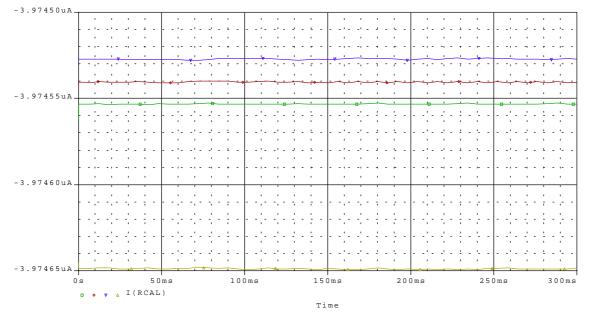

| FIGURE 21 | CALIBRATOR CURRENT SOURCE SIMULATION : VARIATION WITH TEMPERATURE        | 32 |

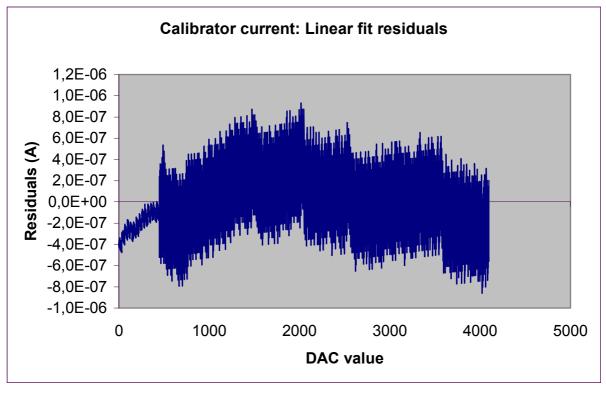

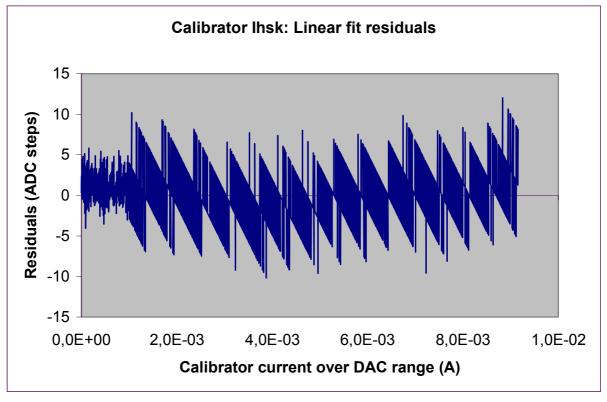

| FIGURE 22 | CALIBRATOR PROTOTYPE : DAC TO CURRENT LINEARITY                          | 33 |

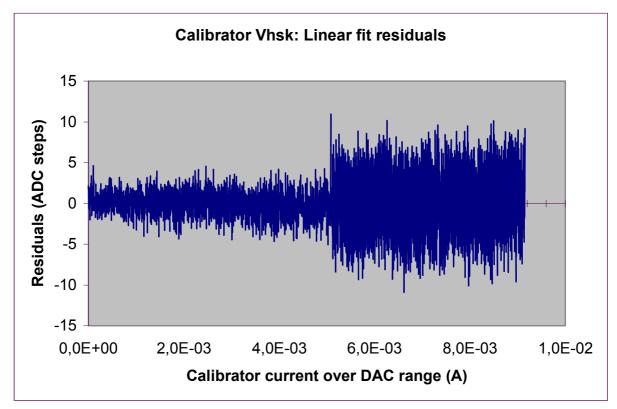

| FIGURE 23 | CALIBRATOR PROTOTYPE : CURRENT TO VHSK LINEARITY                         | 33 |

| FIGURE 24 | CALIBRATOR PROTOTYPE : CURRENT TO IHSK LINEARITY                         | 34 |

| FIGURE 25 | SUB-K BIAS CIRCUIT                                                       | 35 |

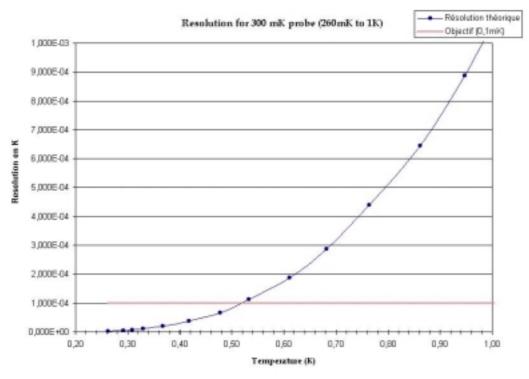

| FIGURE 26 | TEMPAC CIRCUIT : RESOLUTION                                              | 36 |

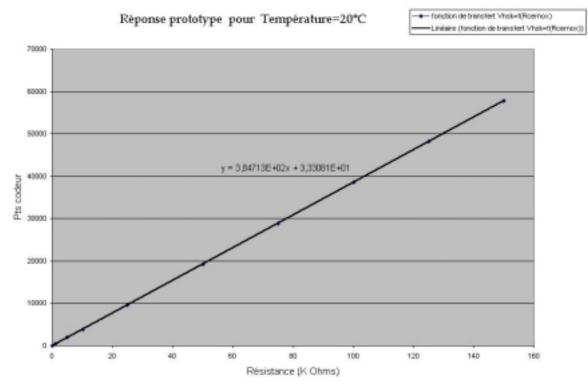

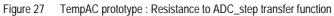

| FIGURE 27 | TEMPAC PROTOTYPE : RESISTANCE TO ADC_STEP TRANSFER FUNCTION              | 37 |

| FIGURE 28 | TEMPAC PROTOTYPE : VARIATION WITH TEMPERATURE                            | 38 |

| FIGURE 29 | TEMPDC CIRCUIT : BLOCK DIAGRAM                                           | 39 |

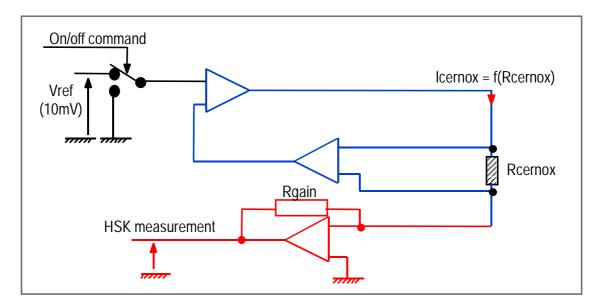

| FIGURE 30 | TEMPDC CIRCUIT : POWER DISSIPATION                                       | 40 |

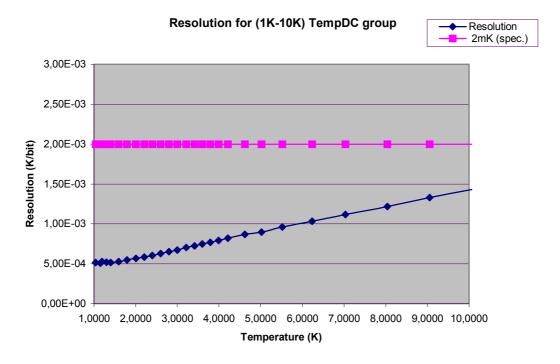

| FIGURE 31 | TEMPDC CIRCUIT : RESOLUTION FOR [1K-10K] GROUP                           | 41 |

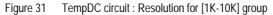

| FIGURE 32 | TEMPDC CIRCUIT : RESOLUTION FOR [3K-300K] GROUP                          | 42 |

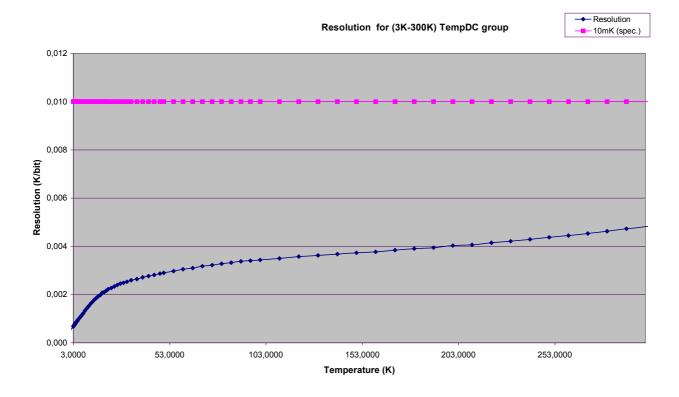

| FIGURE 33 | TEMPDC PROTOTYPE : VHSK VARIATION                                        | 43 |

| FIGURE 34 | TEMPDC PROTOTYPE : VARIATION WITH TEMPERATURE                            | 44 |

| TABLES   |                                                                       |    |

|----------|-----------------------------------------------------------------------|----|

| TABLE 1  | HEATERH REQUIREMENTS                                                  | 11 |

| TABLE 2  | HEATERH PROTOTYPE : MEASUREMENTS                                      | 15 |

| TABLE 3  | HEATERH PROTOTYPE : POWER SUPPLY REJECTION @DAC=287                   | 18 |

| TABLE 4  | HEATERH PROTOTYPE : POWER SUPPLY REJECTION @DAC=2570                  | 18 |

| TABLE 5  | HEATERH PROTOTYPE : TEMPERATURE VARIATION @DAC=3367                   | 19 |

| TABLE 6  | GAS PUMP HEATER SPECIFICATION                                         | 19 |

| TABLE 7  | GAS PUMP HEATER PROTOTYPE : MEASUREMENTS                              | 22 |

| TABLE 8  | GAS PUMP HEATER PROTOTYPE : POWER SUPPLY REJECTION @DAC=\$196         | 23 |

| TABLE 9  | GAS PUMP HEATER PROTOTYPE : POWER SUPPLY REJECTION @DAC=\$E58         | 23 |

| TABLE 10 | GAS PUMP HEATER PROTOTYPE : VARIATION OF HEATER RESISTANCE @DAC=\$FFF | 24 |

| TABLE 11 | THERMAL STRAP HEATER SPECIFICATION                                    | 24 |

| TABLE 12 | PCAL CALIBRATOR SPECIFICATION                                         | 27 |

| TABLE 13 | SCALP CALIBRATOR SPECIFICATION                                        | 27 |

| TABLE 14 | SCALF CALIBRATOR SPECIFICATION                                        | 27 |

| TABLE 15 | CURRENT LIMITATION FOR THE PCAL, SCALP AND SCALF CALIBRATORS          | 29 |

| TABLE 16 | CALIBRATOR CIRCUIT: COMPONENT TEMPERATURE DEPENDENCE                  | 31 |

| TABLE 17 | SCU PARAMETER LIST                                                    | 49 |

| TABLE 18 | SCU DATA FRAME FORMAT                                                 | 50 |

| TABLE 19 | REQUIREMENT CROSS REFERENCE                                           | 52 |

# 1 Introduction

This section gives an overview of the Herschel/SPIRE/DRCU Subsystem Control Unit.

# 1.1 Applicable documents

# 1.1.1 Specification documents

• AD 1 : « DRCU Subsystem Specification », Sap-SPIRE-Cca-0025-00, V0.91 ;

## 1.1.2 Interface documents

- AD 2 : « DRCU Interface Control Document », Sap-SPIRE-Cca-0075-02, V0.6 ;

- AD 3 : « DPU Interface Control Document », SPIRE-IFS-PRJ-650, V1.0.

## 1.1.3 Technical documents

- AD 5 : « A Generic DPU Interface for SPIRE DRCU subsystems », SEDI-SPIRE-OG-0001-02, V0.4.

- AD 6 : « Note on temperature measurement using CERNOX probe for the SPIRE and PACS instruments », C. CARA 28/06/01 ;

# 1.2 Overview

The Subsystem Control Unit (SCU) is an ancillary unit of the DRCU, in charge of various acquisition, control, support and monitoring functions, as specified in AD 1.

# 1.2.1 Acquisition and control functions

The SCU is in charge of the following low-level acquisition and control functions :

- Control and monitoring of the cryo-cooler heaters (recycling heater [SCU-FUNC-01], gas switch heater [SCU-FUNC-02] and FPU thermal strap [SCU-FUNC-03]);

- Control and monitoring of the photometer and spectrometer IR calibrators (PCAL, SCAL Point and SCAL Flood) [SCU-FUNC-04];

- Acquisition of the FPU thermal sensors (thermometry subsystem) [SCU-FUNC-05, -06].

# 1.2.2 Support and monitoring functions

The SCU is in charge of the following low-level support and monitoring functions :

- Logical On/Off control of some PSU secondary power supplies (DCU-LIA P/S, DCU-BIA P/S) [SCU-FUNC-13];

- SCU power supply monitoring [SCU-FUNC-07, -11];

- SCU and PSU electronics temperature monitoring [SCU-FUNC-07, -11].

# 1.2.3 DPU interface functions

To support the above functions, the SCU decodes [SCU-FUNC-08] and responds [SCU-FUNC-11] to DPU commands, according to the DPU Cmd protocol. When in operation, it creates and produces a sequence of measurement Data Frames [SCU-FUNC-12], according to the DPU Data protocol. Each Data Frame carries the value of a relative Time Stamp, which is locally maintained in the SCU [SCU-FUNC-10].

# 2 Architecture

This section gives a general view of the SCU functions and behaviour.

# 2.1 Block diagram

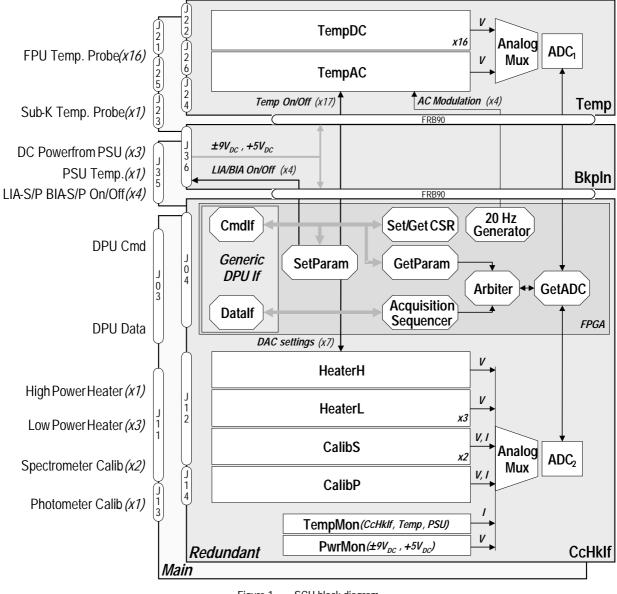

The SCU block diagram is given in Figure 1.

Figure 1 SCU block diagram

The independent single-channel analogue signal conditioning circuits –TempDC, TempAC, HeaterH, HeaterL, CalibS, CalibP, TempMon and PwrMon– are supervised by the SCU Subsystem Logic. This logic is installed in a Field Programmable Gate Array (FPGA) logic cicuit.

CEA/DSM/DAPNIA

# 2.2 Behaviour

The SCU is a slave device running under full supervision of the DPU software. Once initialised, it responds to DPU-initiated commands issued on the *Cmd Interface*. These commands first install the required configuration, and then start SCU operation.

# 2.2.1 Data frame sequence

When in operation, the SCU *Acquisition Sequencer* regularly prepares a well-defined *Data Frame* and autonomously transfers it to the DPU over the *Data Interface*. The frequency and duration of this *Data Frame* sequence are adjustable by configuration. The *Data Frames* are individually time stamped with a local clock value, which is also under control of the DPU software.

## 2.2.2 Subsystem parameter access

Asynchronous commands can be issued by the DPU at any time on the *Cmd* interface, to update or request a SCU parameter value.

#### 2.2.2.1 Parameter update

SCU write-able parameters are updated immediately when the corresponding DPU write command is received and accepted, independent of the activity of the *Acquisition Sequencer*.

#### 2.2.2.2 Parameter request

SCU readable parameters are provided when the corresponding DPU read command is received and accepted. However, the response time depends on the current activity of the *Acquisition Sequencer* when the request is issued. The SCU subsystem logic interleaves the atomic parameter sampling operations corresponding to either cyclic acquisition or asynchronous requests.

# 3 Digital functions

This section describes the functions handled by the FPGA circuit.

# 3.1 Generic DPU Interface

The DPU interface uses an instance of a generic design considered for all three DRCU subsystems (DCU, MCU and SCU). The detailed description of the generic part is given elsewhere (AD 5). Only the main features of this generic block are recalled here, to introduce the description of the SCU-specific control modules.

The generic interface handles the low level serial port protocol of the DPU *Cmd* and *Data* transactions, and presents 2 simple word-oriented interfaces to the subsystem logic :

- On the Cmd side, the subsystem parameter interface provides controlled read/write access to the subsystem parameters, seen as 16-bit words located at specific locations in a 12-bit address space.

- On the Data side, the subsystem data interface is a 16-bit parallel word register on which the subsystem places the individual 16-bit data words of the Data Frame payload in sequence. The encapsulation and transmission of the Data Frame is handled by the generic interface. For each Data Frame, the subsystem logic has the responsibility to signal completion of the payload with a "Last Word" indication. The SCU implementation does not use the optional FIFO mechanism of the generic interface.

# 3.2 SCU Subsystem Logic

Once activated, the SCU Subsystem Logic manages several concurrent threads of control :

- 1. *Acquisition Sequencer* : Automatic periodic parameter measurement, and associated word-perword Data Frame payload construction ;

- 2. *Get Parameter* : On-demand analogue parameter measurement, in response to an individual DPU read command.

- 3. *Get CSR* : On-demand read access to a Control and Status Register (CSR), in response to an individual DPU read command.

- 4. Set Parameter/CSR: On-demand update of an analogue parameter or CSR register, in response to an individual DPU write command.

Operations 1. and 2. require a fresh value of the corresponding parameters, and compete for access to the involved analogue channels. A hardware time scheduling mechanism ensures forward progress for both operations. Operations 3. and 4. do not interfere with 1. and are handled independently.

#### 3.2.1.1 Acquisition Sequencer

When the SCU is started, the *Acquisition Sequencer* schedules a sequence of cyclic acquisitions, and triggers the corresponding *Data Frame* transfers to be produced over the DPU *Data Interface*. The interval between acquisitions and the number of acquisitions expected for a particular operational run are both configured by dedicated parameters.

For each acquisition, the *Acquisition Sequencer* loops over the analogue parameters that are expected in the *Data Frame* payload. Each of them is selected in turn, converted to digital form and presented to the *Subsystem Data* Interface for inclusion in the current packet.

# 4 Analogue functions

This section describes the analogue signal conditioning functions.

# 4.1 Cooler high power heater (HeaterH)

# 4.1.1 Specification

The following table recalls the requirement for the cooler high power heater [extracted from AD 1].

| Туре             | Number | Heater<br>Resistance | Lead resistance | Power       | Max. Voltage | Interface type |

|------------------|--------|----------------------|-----------------|-------------|--------------|----------------|

| Charcoal<br>pump | 1      | 402                  | TBD             | 0 to 500 mW | 15V          | 4-wire         |

Table 1HeaterH requirements

# 4.1.2 General description

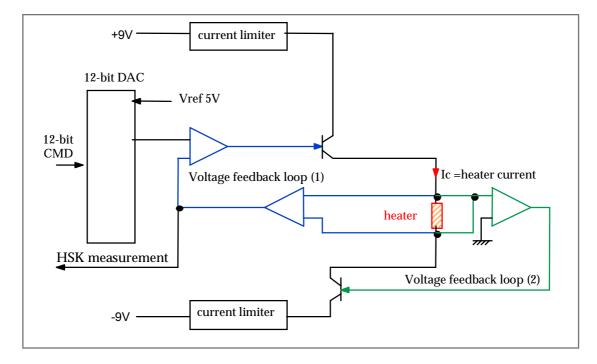

The high power heater is a variable current source controlled by a digital to analogue converter. The system must develop a variable power dissipation in the [0 - 500 mW] range across the heater. With a 402  $\Omega$  heater resistance, the corresponding current range is [0 - 35.3 mA]. The corresponding [0 - 14.2 V] voltage across the heater is measured and made available to the DPU as part of the housekeeping parameters.

The DAC generates a [0 - 5V] voltage used to drive the current source. The current is equilibrated by the heater voltage feedback loop. This voltage is then used for the HSK measurement.

For proper operation at the required 14.2 V heater voltage, bipolar operation is required. A second feedback loop lets the heater voltage develop between the positive and negative power rails.

Two current limiting blocks protect the SCU power supplies against a potential heater short circuit.

Figure 2 Schematic view of the HeaterH circuit

## 4.1.3 Simulation

The following simulations only cover the analogue part of the HeaterH circuit (assuming an ideal D/A converter).

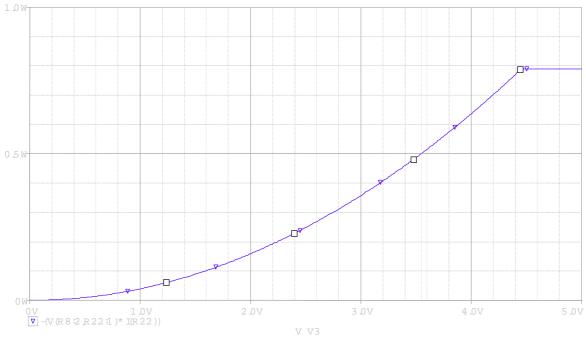

### 4.1.3.1 *Pheater* = *f*(*Ve*)

The maximum heater power (0.5 W) is obtained for a 3.55 V DAC output voltage.

Figure 3 HeaterH simulation : Power variation

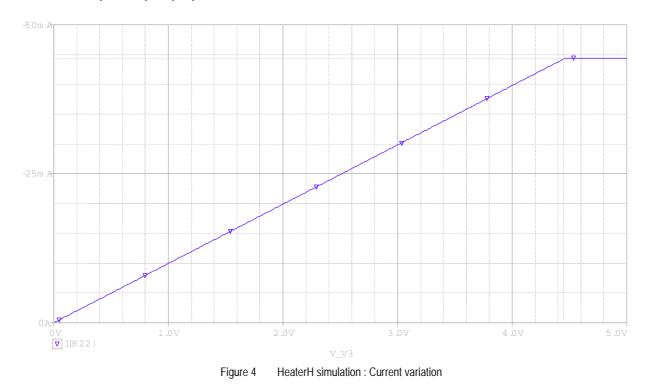

### 4.1.3.2 *lc(heater)* = *f*(Ve)

The transfer function is  $Ic(Heater) = 9,94 E^{-3} mA/V * Ve in the linear range.$

## 4.1.3.3 *Pheater* = f(Vhsk)

Figure 5 HeaterH simulation : Power dissipation vs HSK voltage

#### 4.1.3.4 Residual current for Ve = 0V

For Ve = 0V, we obtain Ic = 466.4 pA.

# 4.1.4 Prototype test results

To validate the HeaterH electronic chain, we developed a prototype circuit with both the analogue and digital sections installed. The performance of this prototype was assessed at several temperatures (0°C, 25°C, 50°C). We verified the power supply rejection and the response to a DAC full swing adjustment step. We measured the circuit over a wide range of heater resistor values and checked the effect of a harness disconnect.

The performance of the analogue section at ambient temperature is :

| Voltage<br>Reference | DAC output<br>voltage Ve(V) | Vheater (V) | Vhsk (V) | lc (A)    |

|----------------------|-----------------------------|-------------|----------|-----------|

| 0                    | 0                           | 20u         | -67u     | 50n       |

| 0.5                  | 0.49999                     | 1.99943     | 0.49804  | 4.998575m |

| 1                    | 1.00004                     | 4.00702     | 0.99804  | 10.01755m |

| 1.5                  | 1.4998                      | 6.01479     | 1.4981   | 15.037m   |

| 2                    | 1.9998                      | 8.02342     | 1.9983   | 20.0585m  |

| 2.5                  | 2.4998                      | 10.0316     | 2.4985   | 25.079m   |

| 3                    | 2.9995                      | 12.03852    | 2.9983   | 30.0963m  |

| 3.5                  | 3.4996                      | 14.04678    | 3.4985   | 35.117m   |

| 4                    | 3.9993                      | 16.05384    | 3.9983   | 40.1346m  |

| 4.5                  | 4.4994                      | 16.57942    | 4.1293   | 41.448m   |

| 5                    | 4.9996                      | 16.57955    | 4.1293   | 41.448m   |

Table 2

HeaterH prototype : Measurements

As expected by simulation, we obtained the specified 500 mW power dissipation for a 3.5V DAC output voltage, and observed saturation at 690 mW. We measured a 50 nA leakage current, leading to a residual 1 pW dissipation in the heater.

#### 4.1.4.1 Transfer function at 25°C

The transfer function at 25°C is as follows :

Figure 6 HeaterH prototype :Current variation

#### 4.1.4.2 Variation with temperature

To evaluate the effect of temperature, we placed the analogue/digital electronic board in a thermal vacuum chamber and measured the heater current and HSK voltage at 0°C, 25°C and 50°C. The measurements were taken for several DAC settings with a nominal 402  $\Omega$  heater resistance.

The DAC output voltage dependence with temperature is as follows :

Figure 7 HeaterH prototype : DAC output voltage dependence with temperature

The DAC output voltage variation is linear with temperature. We find a similar variation on the HSK output, as shown below.

Figure 8 HeaterH prototype : HSK voltage dependence with temperature

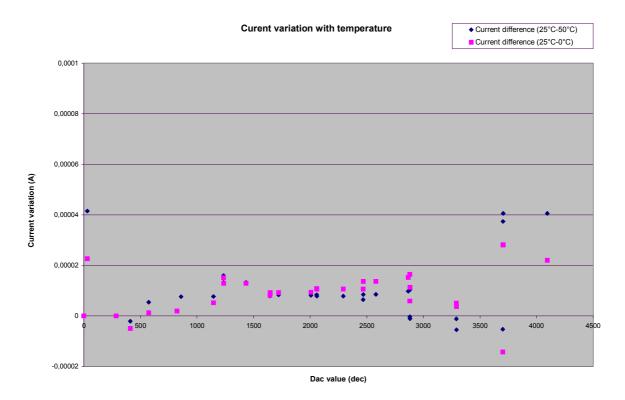

The following figure shows the variation of current at 50°C and 0°C, as compared with the reference temperature ( $25^{\circ}$ C).

Figure 9 HeaterH prototype : Current dependence with temperature

The current dependence on temperature is not identical, but the total dispersion is less than  $100 \,\mu A$  for a 50°C variation. The temperature stability of this design is sufficient for the precision required. If necessary, these systematic effects can be calibrated.

CEA/DSM/DAPNIA

#### 4.1.4.3 Power supply rejection

The power supply rejection is measured at 10% and 90% of the maximum DAC value, with a  $\pm$ 1 V perturbation added to the nominal 9V DC supply. The results are shown in the following tables.

| DAC value | Power<br>supply     | ls          | Relative error (%) | Vhsk    | Vch     |

|-----------|---------------------|-------------|--------------------|---------|---------|

|           | Nominal 9V          | 0.00349925  |                    | 0.34868 | 1.3997  |

| 287 (dec) | Nominal –1V<br>= 8V | 0.003501175 | 0.055              | 0.34887 | 1.40047 |

|           | Nominal +1V<br>=10V | 0.0034973   | -0.055             | 0.34849 | 1.39892 |

Table 3 HeaterH prototype : Power supply rejection @DAC=287

| DAC value | Power<br>supply     | ls        | Relative error (%) | Vhsk   | Vch      |

|-----------|---------------------|-----------|--------------------|--------|----------|

|           | Nominal 9V          | 0.0314975 |                    | 3.1379 | 12.599   |

| 2570(dec) | Nominal –1V<br>= 8V | 0.0314984 | 0.0028             | 3.138  | 12.59936 |

|           | Nominal +1V<br>=10V | 0.0314963 | -0.004             | 3.1378 | 12.59852 |

Table 4

HeaterH prototype : Power supply rejection @DAC=2570

The variation of current in the heater is 0.1% maximum for 2 volts of power supply variation. The power rejection is 0.05%/Volts.

#### 4.1.4.4 Frequency response to a full swing command step

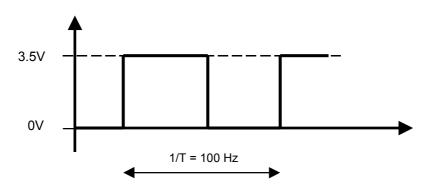

To evaluate the frequency response of the analogue section, we generated a square signal (0 and Imax) at 100 Hz and observed the output voltage with a differential oscilloscope. The frequency response of the electronics is 300 Hz.

#### 4.1.4.5 Variation of the heater resistance

We observed the effect of varying the heater resistance. Keeping the input DAC setting identical, the system parameters were measured for several heater resistance values, including the short and open

circuit conditions. We observed good stability on the actual heater voltage (Vheater) and the housekeeping output (Vhsk), showing the correctness of the voltage control loop and the absence of dependence on the resistance value.

| DAC value  | Rheater<br>intended : actual | DAC output<br>voltage | Vheater  | Vhsk     | ls (Vch/Rch) |

|------------|------------------------------|-----------------------|----------|----------|--------------|

|            | 0 Ω                          | 3.4867                | 0        | 0.000311 | -            |

|            | 400 Ω : 399.3                | 3.48695               | 13.99687 | 3.4859   | 35 m         |

|            | 500 Ω : 497                  | 3.48695               | 13.9962  | 3.486    | 28.16 m      |

| 3367 (dec) | 1000Ω : 1001.3               | 3.48695               | 13.9963  | 3.486    | 13.97 m      |

|            | 1500Ω : 1498.3               | 3.48695               | 13.99637 | 3.486    | 9.34 m       |

|            | 2000Ω : 2004.4               | 3.48695               | 13.9964  | 3.486    | 6.98 m       |

|            | ∞                            | 3.48695               | 13.99648 | 3.486    | 0            |

Table 5

HeaterH prototype : Temperature variation @DAC=3367

The measured short circuit current limitation (Rheater = 0  $\Omega$ ) occurs at 70 mA.

# 4.2 Cooler gas pump heaters (HeaterL)

# 4.2.1 Specification

The following table recalls the requirement for the cooler gas pump low power heaters [extracted from AD 1].

| Туре     | Number | Heater<br>Resistance | Lead resistance | Power    | Max Voltage | Interface type |

|----------|--------|----------------------|-----------------|----------|-------------|----------------|

| Gas pump | 2      | 402                  | TBD             | 0 to 1mW | 15V         | 4-wire         |

Table 6Gas pump heater specification

# 4.2.2 General description

The gas pump low power heater is a variable current source controlled by a digital to analogue converter. The system must develop a variable power dissipation in the [0 - 1 mW] range across the heater. With a 402  $\Omega$  heater resistance, the corresponding current range is [0 - 1.5 mA]. The corresponding [0 - 634 mV] voltage across the heater is measured and made available to the DPU as part of the housekeeping parameters.

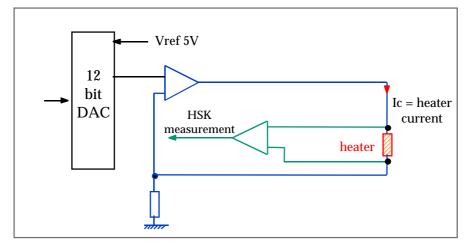

Figure 10 HeaterL circuit : Design principle

The DAC generates a [0 - 5V] voltage used to drive the current source. The current is equilibrated by the heater voltage feedback loop. This voltage is then used for the HSK measurement. The electronic circuit is protected against a potential heater short circuit by a series resistor.

# 4.2.3 Simulation

The following graphs show simulations for the power and current transfer, as function of the DAC output voltage Ve.

## 4.2.3.1 Pheater = f(Ve)

Figure 11 HeaterL simulation : Power variation

## 4.2.3.2 *Iheater* = *f*(*Ve*)

Figure 12 HeaterL simulation : Current variation

The transfer function is Iheater =  $323 \,\mu$ A/V \* Ve in the linear range. The simulated current limiting saturation occurs at 1.6 mA.

#### 4.2.3.3 *Pheater* = *f*(*Vhsk*)

Figure 13 HeaterL simulation : Power dissipation vs HSK voltage

# 4.2.4 Prototype test result

The performance of the analogue section at ambient temperature is :

| Ve  | Vch      | Vhsk     | ls       |

|-----|----------|----------|----------|

| 0   | 40u      | 40u      | 100n     |

| 0.5 | 64.1837m | 383.1m   | 160.459u |

| 1   | 128.409m | 766.19m  | 321u     |

| 1.5 | 192.634m | 1149.27m | 481.585u |

| 2   | 256.89m  | 1532.5m  | 642.22u  |

| 2.5 | 321.134m | 1915.7m  | 802.835u |

| 3   | 385.336m | 2298.7m  | 963.34u  |

| 3.5 | 449.585m | 2681.9m  | 1.124m   |

| 4   | 513.79m  | 3064.8m  | 1.284m   |

| 4.5 | 578.04m  | 3448.1m  | 1.445m   |

| 5   | 642.293m | 3831.3m  | 1.6m     |

Table 7 Gas pump heater prototype : Measurements

The prototype performs as expected by simulation.

#### 4.2.4.1 Transfer function at 25°C

The corresponding linear transfer functions are as follows :

#### Heater current and VHsk as a function of DAC value

Current (A) =  $3.902 E^{-7} * DAC_value - 1.023 E^{-7}$

Hsk (V) = 2386. \* Current + 5.01 E<sup>-4</sup>

Hsk (V) = 9.311  $E^{-4}$  \* Dac\_value - 2,566  $E^{-4}$

The leakage current is 100 nA, corresponding to a minimum dissipation power of 4 pW in the heater.

#### 4.2.4.2 Variation with temperature

The current drift is linear and reaches  $2.5 \,\mu\text{A}$  at  $50^{\circ}\text{C}$  for the maximum current  $1.6 \,\text{mA} (0.0018\%/^{\circ}\text{C})$ . The variation essentially comes from the DAC temperature drift.

Vhsk drifts in the same proportion. If required, the systematic current drift may be corrected from the HSK measurement.

#### 4.2.4.3 Power supply rejection

The power supply rejection is measured at 10% and 90% of the maximum DAC value, with a  $\pm$ 1 V perturbation added to the nominal 9V DC supply. The results are shown in the following tables.

| DAC<br>word | Power<br>Supply (V) | Ve (V)  | Vch (V) | Vhsk (V) | ls (A)    | Relative<br>error (%) |

|-------------|---------------------|---------|---------|----------|-----------|-----------------------|

|             | Nominal 9           | 0.49817 | 63.96m  | 0.38178  | 159.9u    |                       |

| 196h        | 8                   | 0.49815 | 63.96m  | 0.38178  | 159.9u    | 0                     |

|             | 10                  | 0.49818 | 63.965m | 0.38178  | 159.9125u | 0.0078                |

Table 8Gas pump heater prototype : Power supply rejection @DAC=\$196

| DAC<br>word | Power<br>Supply (V) | Ve (V) | Vch (V)  | Vhsk (V) | ls (A)   | Relative<br>error (%) |

|-------------|---------------------|--------|----------|----------|----------|-----------------------|

|             | 9                   | 4.4839 | 0.576028 | 3.4363   | 1.44007m |                       |

| E58h        | 8                   | 4.4838 | 0.576003 | 3.4361   | 1.44m    | -0.0048               |

|             | 10                  | 4.4841 | 0.57604  | 3.4364   | 1.4401m  | 0.002                 |

Table 9 Gas pump heater prototype : Power supply rejection @DAC=\$E58

We observe an excellent rejection, the effect on current being less than 0.01 %.

| DAC<br>word | Heater resistor (R)<br>(intended :actual) | DAC output<br>voltage (V) | V heater (V) | V hsk (V) | ls (A)<br>[Vheater/R] |

|-------------|-------------------------------------------|---------------------------|--------------|-----------|-----------------------|

|             | 0 Ω                                       | 4.9762                    | 40u          | 5.8m      | Limited               |

|             | 400 Ω : 399.3                             | 4.9762                    | 639.253m     | 3.8134    | 1.6009m               |

|             | 500 Ω : 497                               | 4.9762                    | 795.57m      | 4.7446    | 1.6007m               |

| FFFh        | 1000Ω : 1001.3                            | 4.9762                    | 1.60288      | 6.5846    | 1.6007m               |

|             | 1500Ω : 1498.3                            | 4.9762                    | 2.31685      | 6.5652    | 1.546m                |

|             | 2000Ω : 2004.4                            | 4.9762                    | 2.7703       | 6.5655    | 1.3821m               |

|             | ∞                                         | 4.9762                    | 5.6543       | 6.635     | 0                     |

#### 4.2.4.4 Variation of the heater resistance

Table 10 Gas pump heater prototype : Variation of heater resistance @DAC=\$FFF

The current is stable for heater resistances lower than 1 k $\Omega$ . For upper values, the output operational amplifier reaches saturation at  $\approx 6.33$  V. The heater current is limited by a 2 k $\Omega$  resistor. In case of heater short circuit, the harness current is limited to 3.2 mA (6.33 V/2 k $\Omega$ ).

# 4.3 FPU thermal strap heater (HeaterL)

## 4.3.1 Specification

The following table recalls the requirement for the thermal strap low power heaters [extracted from AD 1].

| Туре             | Number | Heater resistance | Lead resistance | Power      | Max. Voltage | Interface type |

|------------------|--------|-------------------|-----------------|------------|--------------|----------------|

| Thermal<br>strap | 1      | ЗК                | TBD             | 300mV/50uA |              | 4-wire         |

Table 11Thermal strap heater specification

## 4.3.2 General description

The FPU thermal strap heater circuit follows the same principle as the gas pump heater circuit. The circuit produces a  $[0 - 50 \ \mu\text{A}]$  current. The maximum power is specified at 7.5  $\mu$ W.

## 4.3.3 Simulation

## 4.3.3.1 *Pheater* = f(Ve)

The maximum power dissipated in the heater (7.5  $\mu$ W) is obtained for a 5V DAC output.

```

4.3.3.2 lc(heater) = f(Ve)

```

<sup>4.3.3.3</sup> Pheater = f(Vhsk)

Figure 17 Thermal strap heater simulation : Power dissipation vs HSK voltage

# 4.3.4 Prototype test result

The results for the FPU thermal strap heater were derived from the low power heater prototype. In this design the leakage current for 0 DAC setting is 100 nA, leading to a residual power dissipation of 30 pW. The heater current is limited by a 50 k $\Omega$  resistor. In case of heater short circuit, the harness current is limited to 126  $\mu$ A.

# 4.4 IR Calibrators : Pcal, ScalP and ScalF

# 4.4.1 Specification

The SCU controls three different calibrators : the photometer calibrator source (PCAL), the spectrometer calibrator point source (SCALP) and the spectrometer calibrator flood source (SCALF).

For each of them, the SCU implements a DAC-controlled current source used to bias the heater resistor of the calibrator source and thus generate a reference IR emission level. The actual current applied to the source resistor and the corresponding voltage are measured, converted to digital form and made available to the DPU.

#### 4.4.1.1 The photometer calibrator (PCAL)

The photometer calibrator consists of a heater mounted in an integrating cavity on the BSM structure. The SCU has to bias this heater according to the dynamic DAC programming sequence provided by the DPU on the *Cmd* interface.

The following table recalls the requirements for the PCAL bias current [extracted from AD 1].

| Heater Bias Current Range            | 0 to 7 mA           | in 4096 steps                    |

|--------------------------------------|---------------------|----------------------------------|

| Maximum dissipated power into heater | 10 mW               |                                  |

| Heater Resistance Range              | 200 to 500 $\Omega$ | +60 $\Omega$ for lead resistance |

| Stability / Repeatability            | 0.5 % or 5 µA       | Whichever is greater             |

| Maximum drive voltage                | 4.0 V               | Worst case                       |

| Bias waveform                        | square              | Spec. for DPU                    |

| Waveform frequency                   | 0 to 5 Hz           | Spec. for DPU                    |

| Waveform resolution                  | 100 ms              | Spec. for DPU                    |

| Interface Type                       | 4-wire              | Supply + sense                   |

Table 12PCAL calibrator specification

#### 4.4.1.2 The spectrometer calibrator point source (SCALP)

The spectrometer calibrator point source consists of a heater mounted on a blackened plate. The SCU has to bias this heater with a variable amplitude.

The following table recalls the requirements for the SCALP bias current [extracted from AD 1].

| Heater Bias Current Range            | 0 to 7 mA       | in 4096 steps                    |

|--------------------------------------|-----------------|----------------------------------|

| Maximum dissipated power into heater | 10 mW           |                                  |

| Heater Resistance Range              | 200 to 500 Ω    | +60 $\Omega$ for lead resistance |

| Stability / Repeatability            | 0.5 % or 5 µA   | Whichever is greater             |

| Maximum drive voltage                | 4.0 V           | Worst case                       |

| Bias waveform                        | DC              |                                  |

| Electrical Interface Type            | 4-wire + shield | Supply + sense                   |

Table 13SCALP calibrator specification

#### 4.4.1.3 The spectrometer calibrator flood source (SCALF)

The following table recalls the requirements for the SCALF bias current [extracted from AD 1].

| Heater Bias Current Range            | 0 to 9 mA     | in 4096 steps                    |

|--------------------------------------|---------------|----------------------------------|

| Maximum dissipated power into heater | 15 mW         |                                  |

| Bias waveform                        | DC            |                                  |

| Stability / Repeatability            | 0.5 % or 5 µA | Whichever is greater             |

| Heater Resistance Range              | 200 Ω         | +60 $\Omega$ for lead resistance |

| Maximum drive voltage                | 5.0 V         |                                  |

| Interface type                       | 2-wire (TBC)  | None connected to ground         |

Table 14SCALF calibrator specification

# 4.4.2 Circuit description

CEA/DSM/DAPNIA

Figure 19 Calibrator current source circuit

#### 4.4.2.1 Current limitation

The calibrator current is limited by the  $R_{\text{lim}}$  resistance at 0.01% of the maximum specified current value.

The value of R<sub>lim</sub> is derived in the following expressions.

First, the maximum dissipated power allowed in the calibrator, the calibrator resistor value and the bias current range  $I_{range}$  give the maximum current  $I_{max}$  expected in the heater.

$$I_{\max} = \sqrt{\frac{P_{\max}}{R_{cal}}}$$

if  $I_{\max} \ge I_{range}$  else  $I_{\max} = I_{range}$

Then,  $I_{max}$  and the the  $V_{ref}$  DAC reference voltage (2.5V) define  $R_{limit}$ .

$$R_{\rm lim} = \frac{V_{ref}}{I_{\rm max}} \times \frac{4095}{4096}$$

The following table gives  $R_{lim}$  for the three different calibrators.

| Function | P <sub>max</sub> | I <sub>range</sub> | R <sub>cal</sub> (Ω) | I <sub>max</sub> | R <sub>lim</sub> (Ω) |

|----------|------------------|--------------------|----------------------|------------------|----------------------|

| PCAL     | 11mW             | 7mA                | 200                  | 7mA (7.4mA)      | 357                  |

| PCAL     | TITTV            | ΛΠΑ                | 500                  | 4.69mA           | 533                  |

| SCALP    | 11mW             | 7mA                | 200                  | 7mA (7.4mA)      | 357                  |

|          |                  |                    | 500                  | 4.69mA           | 533                  |

| SCALF    | 16,5mW           | 9mA                | 200                  | 9mA (9.08mA)     | 277.7                |

Table 15 Current limitation for the PCAL, SCALP and SCALF calibrators

## 4.4.3 Simulation

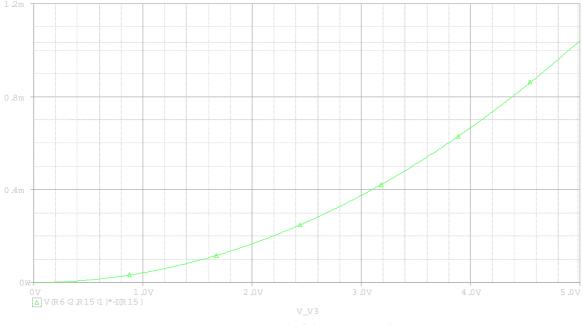

A SPICE simulation was used to verify the operation of the analogue part (from DAC output to I and V measurement).

The design was simulated for the more demanding current drive (Ical = 9 mA), with extreme values for the calibrator resistance (200 and 500  $\Omega$ ). The stimulus applies a voltage ramp from 0 to 2.5 V, then a constant 2.5 V value and finally a decreasing voltage ramp from 2.5 V downto 0 V.

The result is shown on the following graph.

Figure 20 Calibrator current source simulation : Current and Imeas/Vmeas variation

# 4.4.4 Performance requirements

The specification does not specifically asks for absolute calibration, and does not directly define the expected integral and differential linearity. The main requirement is for stability and repeatability, asking for less than 0.5% relative variation over an hour. The main errors that may affect the stability (or repeatability) are the temperature drift and the power supply variations, which both need to be estimated. The maximum residual current that may be accepted when the source is shut off (DAC setting = 0) must also be controlled.

### 4.4.4.1 Residual current estimation

To estimate the residual current, we have to consider the sources of voltage offsets for Vdac :

- DAC leakage current : 50 nA ;

- Offset voltage of the OP27 operational amplifier :  $100 \,\mu V$

$$\delta_{dac} = 50 \quad 10^{9-} \times 15 \quad 10^3 + 3 \times 100 \quad 10^{-6} = 1.05 \quad 10^{-3} (V)$$

We have to add the current bias and offsets of the op-amps used in the current and voltage measurements. For the current measurement the OP-27 op-amp adds 155 nA, for the voltage measurement the OP400 adds 21.5 nA. The corresponding leakage currents are negligible.

#### 4.4.4.2 Variation with temperature : calculation

The following calculations give a first estimate of the current and voltage temperature dependence. A more comprehensive error calculation for the current sources will take place in a further version of the present document.

The estimations of the current ( $\Delta I$ ) and voltage ( $\Delta I$ ) errors are done for the SCALF chain, where the highest current leads to the greatest absolute errors when the 5  $\mu$ A stability / repeatability is expected. For the SCALF chain, the ratio between the current through Rcal and the DAC input code N is :

$$I(Rcal) = 2.228 e^{-6} \times N$$

Each N step corresponds to a 0.61 mV voltage across the Rlim resistor. In the first approach, the errors that are very small compared to this value may be ignored.

The temperature-dependent parameters for all the components involved in the current source circuits are given in the following table.

| Component                | Parameter            | Drift       |

|--------------------------|----------------------|-------------|

| OP27                     | Input offset voltage | 1.8 μV/°C   |

| OP27                     | Input bias current   | ± 0.8 nA/°C |

| OP27                     | Input offset current | 0.75 nA/°C  |

| OP400                    | Input offset voltage | 1.2 μV/°C   |

| OP400                    | Input bias current   | 0.028 nA/°C |

| OP400                    | Input offset current | 0.014 nA/°C |

| DAC AD7545               | Gain                 | ± 5 ppm/°C  |

| ADC ADS7809              | Gain                 | ± 2 ppm/°C  |

| Voltage reference REF-02 | Output voltage       | 8.5 ppm/°C  |

| Resistors                | Resistor value       | 50 ppm/°C   |

Table 16

Calibrator circuit: Component temperature dependence

The current value is I = V/Rlim so  $\Delta I = I * (\Delta V/V + \Delta Rlim/Rlim) = \Delta V/Rlim + I * \Delta Rlim/Rlim, where V is the voltage applied on the Rlim resistor.$

The error on V is due to the current source, the DAC and three OP27 op-amps, for which the offset values and input bias currents flowing in resistors cause drifts. Taking into account the values listed on Table 16 and on the schematic drawing, the resulting  $\Delta V$  error is the following :

$$\Delta V \approx (20e^{-6} + V^* 14e^{-6}) V/^{\circ}C$$

Since Rlim = 274 $\Omega$  and  $\Delta$ Rlim/Rlim = 5e<sup>-5</sup>,  $\Delta$ I  $\approx$  73e<sup>-9</sup> + I \* (14e<sup>-6</sup> +5e<sup>-5</sup>), and we obtain the  $\Delta$ I expression :

∆I ≈ 73e<sup>-9</sup> + I \* 64e<sup>-6</sup> A/°C

As an example, for a full scale current of 9 mA, the temperature drift error is : 0.65  $\mu$ A/°C.

Because the current measurement is achieved by measuring the I \* Rlim2/Rlim voltage, we may assume that the Rlim2/Rlim ratio is not temperature dependent, and thus will not contribute to the error calculation.

Calculating the temperature dependent errors on Imeasured and Vmeasured only needs to add the effects of the OP27 (for Imeasured) and three OP400 input offset voltages and currents, and the gain effects on the output ADC, as listed in Table 16. We obtain :

| $\Delta$ (Vmeasured) = (4.6e <sup>-6</sup> + 2.0 e <sup>-6</sup> * Vmeasured) V/°C |

|------------------------------------------------------------------------------------|

|------------------------------------------------------------------------------------|

and

$\Delta$ (Imeasured) = ((3.35e-6 + 2.0 e-6 \* Imeasured\*Rlim2)/Rlim2) A/°C

The Rlim2 value is : Rlim2 = 274  $\Omega$ .

#### 4.4.4.3 Variation with temperature : simulation

The temperature variation rate is expected to be lower than 3 K/h. The following simulation shows the current variation for T = 0°, 24°, 27°, and 30°C.

Figure 21 Calibrator current source simulation : Variation with temperature

## 4.4.5 Prototype test results

A prototype circuit was developed for the calibrator circuit. This circuit includes the DAC, the analogue circuitry, the ADC, and a FPGA for the logic interface with a Personal Computer. The current across the resistive load is measured with an external high precision GPIB-driven instrument.

The following graphs show recent measurements giving the linearity of the current production, and the linearity of the voltage and current housekeeping measurements. These results are very preliminary and require further analysis and discussion.

#### 4.4.5.1 DAC to current linearity

Figure 22 Calibrator prototype : DAC to current linearity

#### 4.4.5.2 Voltage measurement linearity

Figure 23 Calibrator prototype : Current to VHSK linearity

#### 4.4.5.3 Current measurement linearity

Figure 24 Calibrator prototype : Current to IHSK linearity

# 4.5 Sub-K thermometry : TempAC

# 4.5.1 Specification

As extracted from AD 1.

# 4.5.2 Design principle

The resistance variation [R = f(T)] of the Cernox CX-1030 sensor shows a very strong dR/dT for temperatures lower than 2 K. To obtain the required 0.1 mK resolution at T = 300 mK, a high gain is necessary in the measurement chain. To cancel the low-frequency accumulated offset and temperature drift errors, a differential measurement is implemented. The sensor is AC biased at 20 Hz, and the measurements are synchronous with the AC excitation. Each temperature point results from the differential combination of two measurements taken synchronously with the 2 phases of the AC excitation. This measurement chain was developed in collaboration with the *Service de Basses Températures* (CEA/SBT).

The sensor is current biased, in order to obtain a broad measurement range (up to 10 K) with sufficient resolution while controlling the dissipation at the nominal 300 mK operating point. The selected bias current value is 40 nA. At the operating temperature, the corresponding self-heating error is lower than 1 mK (to be compared with the 5 mK precision of the Cernox R(T) transfer curve).

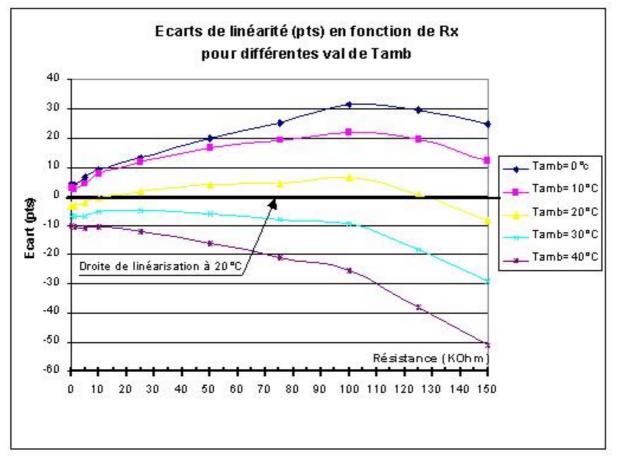

## 4.5.3 Block diagram

Figure 25 Sub-K bias circuit

The sensor current (Icernox) is a square waveform obtained by current steering from a stable current source (Is). The steering operation is driven by a 20 Hz digital square wave modulation command, alternately injecting +Is and –Is into the Cernox sensor. After amplification, the voltages corresponding to the positive and negative current phases are sampled and held in correlation with the steering command, and then passed to a differential analogue stage to produce the Vhsk measurement. The low frequency error contributions (LFErr) are suppressed by this method, Vhsk being Vcernox\*G+LFErr – (-Vcernox\*G+LFErr) = 2\*G\*Vcernox. This alternative measurement technique theoretically cancels the errors caused by bias currents, offset voltages and very low frequency noise sources.

## 4.5.4 Resolution

The Cooler Evaporator sensor must be sensitive in the [0.25K-10K] temperature range, with 0.1 mK resolution. Taking into account the R(T) response of the Cernox sensor, the expected resolution in the [260mK-1K] range is given in the following graph, computed with G = 800.

### 4.5.4.1 Expected resolution

Figure 26 TempAC circuit : Resolution

The requirement for 0.1 mK resolution is easily fulfilled in the operating region (between 250 mK and 550 mK). For higher temperatures, the resolution degrades (1 mK@1K, 0.3K@10K) but is sufficient for gross temperature monitoring.

Due to the current bias technique, the voltage measurement chain may saturate at low temperatures, where the sensor resistance gets very large. The circuit is designed to operate linearly when the sensor resistance does not exceed 150 k $\Omega$ . This figure was selected to give sufficient margin from the Lakeshore specification, which gives R<100 k $\Omega$  @300mK.

## 4.5.5 Prototype measurements

To validate the TempAC electronic chain, we developed a prototype circuit with both the analogue and ADC sections installed. The linearity of the voltage measurement was verified over the full variation range of the Cernox resistance value. The performance of the prototype was assessed at several temperatures ( $0^{\circ}$ ,  $10^{\circ}$ ,  $20^{\circ}$ ,  $30^{\circ}$  and  $40^{\circ}$ C).

### 4.5.5.1 Vhsk = f(Rcernox)

The response curve was measured for several reference resistance values, chosen to cover the expected Cernox resistance variation range. The measurement confirms the linearity and the absence of saturation for resistance values as high as 150 k $\Omega$ . The measured slope is 384 ADC\_steps/k $\Omega$ . The corresponding resolution is 3  $\mu$ K/ADC\_step @300 mK (R= 65 k $\Omega$ , dR/dT(mK) = 1000).

#### 4.5.5.2 Variation with temperature

Figure 28 TempAC prototype : Variation with temperature

The above graph shows the variation of the response (expressed in ADC steps) when the circuit is placed at T= 0, 10, 20, 30 and 40°C. At R = 65 k $\Omega$ , a 40°C temperature variation displaces the response by 40 ADC steps, which corresponds to a brute error of 0.12 mK. The expected temperature variation of the electronics is much smaller, and compensation will normally be unnecessary; if required, this systematic error could however be calibrated and compensated.

# 4.6 Other thermometry channels: TempDC

## 4.6.1 Specification

As extracted from AD 1.

## 4.6.2 Design principle

The TempDC circuit produces a fixed voltage bias across the Cernox CX-1030 sensor. The sensor current is measured by a simple current to voltage conversion, and reflects the resistance variation. The calibrated transfer function [R = f(T)] of the Cernox sensor is then used to obtain the temperature.

The rationale for the selection of the voltage bias technique is to obtain a slowly varying resolution over a broad measurement range, the Vhsk = k/R transfer function compensating the strong non-linearity of R(T) at low T values. A more involved discussion can be found in AD 6.

Figure 29 TempDC circuit : Block diagram

The HSK voltage is measured by a 16-bit ADC. The value of the Cernox resistance is derived from the current to voltage conversion formula : Vhsk = - Rgain \* (Vref / Rcernox).

### 4.6.2.1 Bias voltage determination

The power dissipated in the sensor produces self-heating, which in turn disturbs the actual temperature measurement. This perturbation is difficult to estimate because the involved thermal impedance depends on several effects (material used in the sensor, thermalisation of the sensor, etc.). The selected bias voltage was defined after measurements obtained from the CEA/SBT. These measurements are shown in the following graph.

Figure 30 TempDC circuit : Power dissipation

The graph shows the power dissipation level that would create a 1 mK displacement error on the temperature reading (above), and the actual dissipation produced by the circuit when biased at 10 mV (below). Over the full temperature range of the sensor, the dissipation when applying a 10 mV bias is sufficiently small to produce a self-heating error lower than 1 mK (to be compared with the 5 mK precision of the Cernox R(T) transfer curve).

## 4.6.3 Resolution

The 16 sensors measured by the TempDC circuit pertain to 2 distinct groups : The low temperature group (1 K – 10 K, 2 mK resolution @1 K), and the extended temperature group (3 K – 300 K, 10 mK resolution @3 K).

The Cernox sensor R(T) variation is strongly non-linear with temperature. Knowing the constant Vbias and the R(T) characteristic curve, the gain of the trans-impedance amplifier must be adjusted to obtain the required resolution at the lower end of the corresponding temperature range, and stay in the 5 V full scale of the 16-bit ADC. The following graphs show the obtained resolution for each group.

### 4.6.3.1 Expected resolution (low temp. group)

The above graph shows the evolution of the resolution over the low temperature range (below), as compared with the required resolution (above). The requirement is fulfilled over the full range. The current to voltage gain resistance is 54 k $\Omega$ .

### 4.6.3.2 Expected resolution (extended temp. group)

Figure 32 TempDC circuit : Resolution for [3K-300K] group

The above graph shows the evolution of the resolution over the extended temperature range (below), as compared with the required resolution (above). The requirement is fulfilled over the full range. The current to voltage gain resistance is  $15 \text{ k}\Omega$ .

## 4.6.4 Prototype measurement

A dedicated TempDC prototype circuit was implemented, to validate the circuit principle and study the temperature variation.

### 4.6.4.1 *Vhsk* = *f*(*Rcernox*)

Figure 33 TempDC prototype : Vhsk variation

The above graph shows the evolution of Vhsk when the load resistance varies from 4 K $\Omega$  to 100  $\Omega$  (corresponding to a temperature variation from 1 K to 65 K on a typical Cernox sensor). The sensitivity is stronger for small resistor values (k/R dependence). This effect somewhat compensates the Cernox non-linearity, which is stronger for high resistor values.

The Vhsk precision directly depends on the precision of the current-to-voltage gain resistance value (Rgain). The precision of Rgain is 0.1% on the prototype, and will be improved to 0.01% on the flight model. The measurement chain will require calibration to maintain this precision.

### 4.6.4.2 Variation with temperature

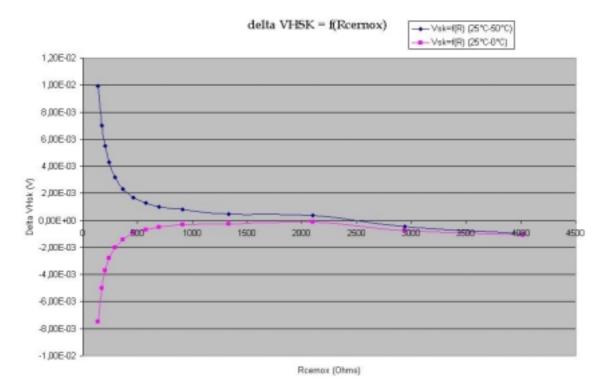

Figure 34 TempDC prototype :Variation with temperature

The above graph shows the variation of Vhsk at 0°C and 50°C as compared with the reference measurement @25°C. The curves show a symmetric spread, proportional to Vhsk. Here again, the temperature behavior could be calibrated and compensated if necessary.

# 4.7 Electronics Temp. Monitor : TempMon

As specified in AD 1, the electronics temperature monitoring channels use the AD590 sensor, connected to a simple current to voltage converter. They are read out through the common ADC system (ADC2 in Figure 1).

The detailed circuit description and associated performance analysis (vs. DCU-REQ-81) will be added when available.

## 4.8 Power Supply Monitor : PwrMon

The power supply monitoring channels use simple voltage followers, and are readout through the common ADC system (ADC2 in Figure 1).

The detailed circuit description and associated performance analysis (vs. DCU-REQ-83) will be added when available.

# **5** Physical implementation

This section covers the actual details of the physical implementation : boards, connectors, pinouts, etc.

# 5.1 Boards

In conformance with the specified mechanical requirements (AD 2-Section 3.), the SCU module is implemented as a set of 2 active electronic boards (*Temp* and *CcHkIf*), interconnected with a dedicated passive printed circuit backplane (*BkpIn*).

Two identical SCU modules (*Main and Redundant*) are installed in the SCU compartment of the FCU box (see Figure 1).

# 5.2 Backplane

## 5.2.1 PSU interconnects

The BkpIn board receives from PSU :

- The secondary power supplies required by the SCU;

- An analogue temperature sensing level used to monitor the internal temperature of the PSU electronics.

The BkpIn board provides to PSU :

• The On/Off logical power break signals required to control the DCU LIA\_P, LIA\_S, BIAS\_P and BIAS\_S secondary power supplies.

These signals are exchanged over the J35(M) / J36(R) side connectors of the SCU.

## 5.2.2 Board interconnects

Two FRB90 connectors insure electrical and mechanical connection between the Bkpln and Temp / Cchklf boards.

### 5.2.2.1 Bkpln/Temp connector

The actual connector signal list will be added when available.

### 5.2.2.2 Bkpln/Cchklf connector

The actual connector signal list will be added when available.

# 5.3 Temp board

The physical implementation of the Temp board will be added when available.

# 5.4 CCHklf board

The physical implementation of the Cchklf board will be added when available.

# 6 Operation

This section describes the programming model of the SCU, and the phases required to operate it.

# 6.1 Working cycle

The SCU runs under supervision of the DPU software.

At power on, the SCU takes a definite Reset state for a short time, and then autonomously leaves this state without DPU intervention. The DPU software can later place the SCU in its Reset state, by writing the Subsystem Reset bit in a control register.

In a typical session, the DPU first installs the required configuration for the operational run, and then launches the SCU frame sequence for a limited or infinite time. During operation, the DPU software has unhindered access to all CSR registers and analogue parameters. Once out of Reset, the SCU is stateless and does not apply censorship on DPU transactions. Potential problems may be expected if the DPU changes configuration while a frame sequence is running. The SCU does not include any special mechanism to detect, log or reject incorrect DPU software sequences.

## 6.2 Parameter list

The following table gives the current state of the SCU parameter list.

| Name <sup>1</sup>                | Address <sup>2</sup>               | Type <sup>3</sup> | Parameter format <sup>4</sup>               | Comment                                                     | Default⁵ |  |

|----------------------------------|------------------------------------|-------------------|---------------------------------------------|-------------------------------------------------------------|----------|--|

| Interface Registers <sup>6</sup> |                                    |                   |                                             |                                                             |          |  |

| CmdlfStat                        | 000 000000                         | R                 | R: 0000 0000 00VV VVVV                      | Return interface status                                     | \$0000   |  |

| CmdlfCtrl                        | 000 000001                         | BWR               | W:VVV<br>R: 0000 0000 0000 0VVV             | Set / return interface controls (active low resets)         | \$0003   |  |

| SubSDelay                        | 000 000010                         | R                 | R: 0000 000V VVVV VVVV                      | Return Subsystem response time                              | \$01FF   |  |

| TStampRst                        | 000 000011                         | BW                | W:                                          | Reset time stamp                                            | NA       |  |

| Unmapped A                       | Area                               |                   |                                             |                                                             |          |  |

| Unknown1                         | 0001                               | NA                | Not Applicable                              | Used to test timeout on unknown address                     | NA       |  |

| Unknown2                         | 001                                | NA                | Not Applicable                              | Used to test timeout on unknown address                     | NA       |  |

| Unknown3                         | 01                                 | NA                | Not Applicable                              | Used to test timeout on unknown address                     | NA       |  |

| Configuratio                     | Configuration and Status Registers |                   |                                             |                                                             |          |  |

| ScuStatus                        | 100000                             | R                 | R: Not yet defined                          | Return Subsystem status                                     | \$0000   |  |

| FrRequest                        | 100001                             | W                 | W:                                          | Initiate frame sequence transfer                            | NA       |  |

| FrameStop                        | 100010                             | W                 | W:                                          | Stop frame sequence transfer                                | NA       |  |

| FrameConf                        | 100011                             | WR                | W: V VVVV VVVV<br>R: V000 0000 VVVV VVVV    | Set / return frame config (type + rate)                     | \$0000   |  |

| SeqLength                        | 100100                             | WR                | W: VVVV<br>R: 0000 0000 0000 VVVV           | Set / return number of frames per sequence $(0 = infinite)$ | \$0000   |  |

| TempOnOff                        | 100101                             | WR                | W: VVVV VVVV VVVV VVVV<br>R: VVVV VVVV VVVV | Set / return FPU temperature probe bias On/Off state        | \$0000   |  |

| SubKOnOff                        | 100110                             | WR                | W:V<br>R: 0000 0000 0000 000V               | Set / return sub K temperature probe bias On/Off state      | \$0000   |  |

| DRelOnOff                        | 100111                             | WR                | W: VVVV<br>R: 0000 0000 0000 VVVV           | Set / return LIA and BIA power relays On/Off state          | \$0000   |  |

| TReserved                        | 101                                | NA                | lp                                          | Reserved for test                                           | NA       |  |

| CcHklf analogue resources        |                                    |                   |                                             |                                                             |          |  |

| LHeaterIV1                       | 1100 -000                          | WR                | W: IIII IIII IIII<br>R: VVVV VVVV VVVV VVVV | Set current / measure voltage of Low Power Heater 1         | Note 7,8 |  |

| LHeaterIV2                       | 1100 -001                          | WR                | W: IIII IIII IIII<br>R: VVVV VVVV VVVV VVVV | Set current / measure voltage of Low Power Heater 2         | Note 7,8 |  |

| LHeaterIV3                       | 1100 -010                          | WR                | W: IIII IIII IIII<br>R: VVVV VVVV VVVV VVVV | Set current / measure voltage of Low Power Heater 3         | Note 7,8 |  |

| HHeaterIV1                       | 1100 -011                          | WR                | W: IIII IIII IIII<br>R: VVVV VVVV VVVV VVVV | Set current / measure voltage of High Power Heater          | Note 7,8 |  |

| CsuTempRd                        | 1100 -100                          | R                 | R: VVVV VVVV VVVV VVVV                      | Measure CcHkIf board temperature                            | NA       |  |

| TsuTempRd                        | 1100 -101                          | R                 | R: VVVV VVVV VVVV VVVV                      | Measure TEMP board temperature                              | NA       |  |

| PsuTempRd                        | 1100 -110                          | R                 | R: VVVV VVVV VVVV VVVV                      | Measure PSU temperature                                     | NA       |  |

| ScuCHTp05                        | 1100 -111                          | R                 | R: VVVV VVVV VVVV VVVV                      | Measure +05VDC power supply                                 | NA       |  |

<sup>1</sup> Parameters are listed in ascending address order.

CEA/DSM/DAPNIA

The Subsystem Control Unit (SCU)

<sup>&</sup>lt;sup>2</sup> The "-" character denotes a don't care bit.

<sup>&</sup>lt;sup>3</sup> B : supports broadcast write access ; W : supports write access; R : supports read access ; F : eligible for inclusion in the Data Frame ; NA : Not Applicable.

$<sup>^{4}</sup>$  The "-" character denotes a don't care bit ; The "v" character denotes a valid bit.

<sup>&</sup>lt;sup>5</sup> The default value is obtained at Power On or after a Subsystem Reset command ; \$hhhh indicates hexadecimal format ; NA : Not Applicable.

<sup>&</sup>lt;sup>6</sup> Refer to AD 2 for details.

<sup>&</sup>lt;sup>7</sup> The DAC is automatically placed to its lower possible value (\$000) at Power On or Subsystem Reset.

<sup>&</sup>lt;sup>8</sup> The read operation measures the voltage corresponding to DAC setting = \$000.

| Name <sup>1</sup> | Address <sup>2</sup>    | Type <sup>3</sup> | Parameter format <sup>4</sup>               | Comment                                               | Default <sup>5</sup>  |

|-------------------|-------------------------|-------------------|---------------------------------------------|-------------------------------------------------------|-----------------------|

| ScuCHTn09         | 1101 -000               | R16               | R: VVVV VVVV VVVV VVVV                      | Measure -09VDC power supply                           | NA                    |

| ScuCHTp09         | 1101 -001               | R                 | R: VVVV VVVV VVVV VVVV                      | Measure +09VDC power supply                           | NA                    |

| Calibral1         | 1101 -010               | WRF               | W: IIII IIII IIII<br>R: VVVV VVVV VVVV VVVV | Set / measure current applied to Calibration source 1 | Note 7,9              |

| CalibraV1         | 1101 -011               | RF                | R: VVVV VVVV VVVV VVVV                      | Measure voltage of Calibration source 1               | Note 7,8              |

| Calibral2         | 1101 -100               | WRF               | W: IIII IIII IIII<br>R: VVVV VVVV VVVV VVVV | Set / measure current applied to Calibration source 2 | Note 7,9              |

| CalibraV2         | 1101 -101               | RF                | R: VVVV VVVV VVVV VVVV                      | Measure voltage of Calibration source 2               | Note 7,8              |

| Calibral3         | 1101 -110               | WRF               | W: IIII IIII IIII<br>R: VVVV VVVV VVVV VVVV | Set / measure current applied to Calibration source 3 | Note 7,9              |

| CalibraV3         | 1101 -111               | RF                | R: VVVV VVVV VVVV VVVV                      | Measure voltage of Calibration source 3               | Note 7,8              |

| Temp analog       | Temp analogue resources |                   |                                             |                                                       |                       |

| FpuTemp01         | 1110 0000               | RF                | R: VVVV VVVV VVVV VVVV                      | Measure FPU probe 01 temperature                      | Note <sup>10,11</sup> |

| FpuTemp02         | 1110 0001               | RF                | R: VVVV VVVV VVVV VVVV                      | Measure FPU probe 02 temperature                      | Note <sup>10,11</sup> |

| FpuTemp03         | 1110 0010               | RF                | R: VVVV VVVV VVVV VVVV                      | Measure FPU probe 03 temperature                      | Note <sup>10,11</sup> |

| FpuTemp04         | 1110 0011               | RF                | R: VVVV VVVV VVVV VVVV                      | Measure FPU probe 04 temperature                      | Note <sup>10,11</sup> |

| FpuTemp05         | 1110 0100               | RF                | R: VVVV VVVV VVVV VVVV                      | Measure FPU probe 05 temperature                      | Note <sup>10,11</sup> |

| FpuTemp06         | 1110 0101               | RF                | R: VVVV VVVV VVVV VVVV                      | Measure FPU probe 06 temperature                      | Note <sup>10,11</sup> |

| FpuTemp07         | 1110 0110               | RF                | R: VVVV VVVV VVVV VVVV                      | Measure FPU probe 07 temperature                      | Note <sup>10,11</sup> |

| FpuTemp08         | 1110 0111               | RF                | R: VVVV VVVV VVVV VVVV                      | Measure FPU probe 08 temperature                      | Note <sup>10,11</sup> |

| FpuTemp09         | 1110 1000               | RF                | R: VVVV VVVV VVVV VVVV                      | Measure FPU probe 09 temperature                      | Note <sup>10,11</sup> |