# SPIRE

| SUBJECT:     | FIRST SPIRE DPU Subsystem Specification Document |       |                 |

|--------------|--------------------------------------------------|-------|-----------------|

| PREPARED BY: | A.M. Di Giorgio, R. Cerulli-Irelli, R.           | Orfei |                 |

| DOCUMENT No: | SPIRE-IFS-PRJ-000462                             |       |                 |

| ISSUE:       | 1.1                                              | Date: | 26th March 2001 |

| APPROVED BY:           | Date:                   |

|------------------------|-------------------------|

| Local Project Manager: | Riccardo Cerulli-Irelli |

| Project Manager:       | Ken King                |

| Instrument Scientist:  | Bruce Swinyard          |

| Systems Engineer:      | John Delderfield        |

| Local Co-Investigator: | Paolo Saraceno          |

**REFERENCE:**

FIRST SPIRE DPU Subsystem Specification Document

Ref.:

SPIRE-IFS-PRJ-000462

Issue:

Issue 1.1

Date:

26/03/2001

Page:

Page 1 of 24

## FIRST SPIRE

# **DPU** Subsystem Specification Document

#### Document Ref.: SPIRE-IFS-PRJ-000462

Issue: Issue 1.1

Prepared by: Anna Maria Di Giorgio Riccardo Cerulli-Irelli Renato Orfei Date: 26/03/2001

#### **Distribution List :**

| RAL     | B.M.Swinyard |

|---------|--------------|

|         | K.King       |

| IFSI    | S. Pezzuto   |

|         | C. Codella   |

| CEA-Sap | JL. Auguères |

|         | C. Cara      |

Istituto di Fisica dello Spazio Interplanetario – CNR Area di Ricerca Tor Vergata Via del Fosso del Cavaliere 00133 Roma Tel.: (39) 06 4993 4490 – Fax: (39) 06 4993 4383

Ref.:

SPIRE-IFS-PRJ-000462

Issue:

Issue 1.1

Date:

26/03/2001

Page:

Page 2 of 24

| 1 | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | .5                                                                                           |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

|   | 1.1 PURPOSE OF THE DOCUMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | .5                                                                                           |

| 2 | DOCUMENT LIST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | .5                                                                                           |

|   | <ul> <li>2.1 APPLICABLE DOCUMENTS</li> <li>2.2 REFERENCE DOCUMENTS</li> <li>2.3 ACRONYMS AND GLOSSARY</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                 | .5<br>.6                                                                                     |

| 3 | SUBSYSTEM DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | .7                                                                                           |

|   | 3.1       General Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | .9<br>14                                                                                     |

| 4 | SPECIFICATIONS1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15                                                                                           |

|   | 4.1FUNCTIONAL SPECIFICATIONS14.1.1Performance specifications14.1.2Technical specifications14.1.2Technical specifications14.2Operational Safety14.2.1Operational Safety14.2.2Lifetime14.2.3Telemetry14.2.4Telecommands14.3INTERFACE REQUIREMENTS14.4Design and MANUFACTURING SPECIFICATIONS14.4.1Design requirements14.4.2Design rules24.4.3Manufacture Requirements24.4.3Manufacture Requirements24.6ENVIRONMENT REQUIREMENTS24.6.1Natural environment24.6.2Operating Environment24.7VERIFICATION REQUIREMENTS2 | 15<br>15<br>16<br>16<br>16<br>16<br>17<br>19<br>19<br>21<br>22<br>22<br>22<br>22<br>22<br>22 |

|   | 4.7.1 DPU Acceptance And Qualification2                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                              |

| A | PPENDIX 1: QUALIFICATION TESTS DESCRIPTION2                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 24                                                                                           |

# **Document Status Sheet:**

| Document Title: FIRST SPIRE DPU Subsystem Specification Document |          |              |                                          |

|------------------------------------------------------------------|----------|--------------|------------------------------------------|

| Issue                                                            | Revision | Date         | Reason for Change                        |

| Draft 1                                                          |          | 23 May 2000  | First draft                              |

| Draft 2                                                          |          | 13 June 2000 | Updated accordingly to new Issues of the |

|                                                                  |          |              | Applicable Documents                     |

| Issue 1.0                                                        |          | 24 Nov 2000  | First Issue, updated accordingly to new  |

|                                                                  |          |              | Issues of the Applicable Documents       |

| Issue 1.0                                                        | 0.1      | 26 Mar 2001  | Updated accordingly to new Issues of the |

|                                                                  |          |              | Applicable Documents. Low speed          |

|                                                                  |          |              | interface protocol updated.              |

# **Document Change Record:**

| Document Title: FIRST SPIRE DPU Subsystem Specification Document |                                                           |  |

|------------------------------------------------------------------|-----------------------------------------------------------|--|

| Document Reference Number: SPIRE-IFS-PRJ-000462                  |                                                           |  |

| Section                                                          | Reason For Change                                         |  |

| 3.2, page 13                                                     | New Low Speed Interface Protocol Description              |  |

| 3.2, fig. 3-10                                                   | New Low Speed Interface Protocol graphical representation |  |

| 3.2, fig. 3-4                                                    | New CPU memory organisation scheme                        |  |

| 4.4.1, DPU-DES-32                                                | New DPU mechanical dimensions.                            |  |

# **1** Introduction

## **1.1 Purpose of the document**

The Istituto di Fisica per lo Spazio Interplanetario (IFSI) of the Italian Consiglio Nazionale delle Ricerche (CNR) is responsible for the design and manufacturing of the three Digital Processing Units/Instrument Control Units for the three instruments to be flown on board of the ESA satellite FIRST: HIFI, PACS and SPIRE.

This specification defines the requirements applied to the performances, the design and the qualification of the SPIRE Digital Processing Unit (FSDPU subsystem). It is applicable to the AVM, the QM, the PFM and the FS.

The DPU On Board Software specification is given in the DPU/ICU OBS User Requirements Document and DPU/ICU OBS Software Specification Document.

# 2 Document List

#### **2.1 Applicable Documents**

| Document  | Name                                              | Number/version/date        |  |

|-----------|---------------------------------------------------|----------------------------|--|

| Reference |                                                   |                            |  |

| AD1       | SPIRE Instrument Requirements Document            | SPIRE/RAL/N/0034           |  |

|           | <b>1</b>                                          | Issue 0.1 23 Nov 2000      |  |

| AD2       | FIRST/Planck Instrument Interface Document Part A | PT-IID-A-04624             |  |

|           |                                                   | Draft 0.3 15 May 2000      |  |

| AD3       | FIRST/Planck Instrument Interface Document Part B | SCI-PT-IIDB/PT-SPIRE-02124 |  |

|           | Instrument "SPIRE"                                | Issue 0.1 01 Sep 2000      |  |

| AD4       | Operating Modes for the SPIRE Instrument          | SPIRE-RAL-DOC-000320       |  |

|           |                                                   | Issue 0.22 14 June 2000    |  |

| AD5       | FIRST L-2 Radiation Environment                   | SPIRE-ESA-DOC-000195       |  |

| AD6       | DPU Interface Control Document                    | SPIRE-IFS-DOC              |  |

|           |                                                   | Issue 0.1 22 Nov 2000      |  |

## **2.2 Reference Documents**

| Document<br>Reference | Name                                                                 | Number/version                                 |  |

|-----------------------|----------------------------------------------------------------------|------------------------------------------------|--|

| RD1                   | DPU/DRCU Interface Control Document                                  | SPIRE-SAP-PRJ-000451<br>Issue 0.2 21 June 2000 |  |

| RD2                   | Discussion Note on the DPU/DRCU Operations<br>Protocols- B. Swinyard | 22 May 2000                                    |  |

DPU Subsystem Specification

Ref.:

SPIRE-IFS-PRJ-000462

Issue:

Issue 1.1

Date:

26/03/2001

Page:

Page 6 of 24

Document

## 2.3 Acronyms and Glossary

#### 2.3.1 Acronyms

| AD     | Architectural Design                                |

|--------|-----------------------------------------------------|

| ATP    | Acceptance Test Plan                                |

| AVM    | Avionic Model                                       |

| CNR    | Consiglio Nazionale delle Ricerche                  |

| CPU    | Control Processing Unit                             |

| CDMS   | Computer Data Management System                     |

| CPP    | Common parts Procurement                            |

| CQM    | Cryogenic Qualification Model                       |

| DDD    | Detailed Design Document                            |

| DPU    | Digital Processing Unit                             |

| DSP    | Digital Signal Processor                            |

| EEPROM | Electrically Erasable Programmable Read Only Memory |

| EMC    | ElectroMagnetic Compatibility                       |

| EMI    | ElectroMagnetic Interference                        |

| ESA    | European Space Agency                               |

| FIRST  | Far InfraRed and Submillimeter Telescope            |

| HIFI   | Heterodyne Instrument for FIRST                     |

| HK     | HouseKeeping                                        |

| HW     | HardWare                                            |

| IBDR   | Instrument Baseline Design Review                   |

| ICD    | Interface Control Document                          |

| ICDR   | Instrument Critical Design Review                   |

| ICU    | Instrument Control Unit                             |

| IHDR   | Instrument Hardware Design Review                   |

| IFSI   | Istituto di Fisica dello Spazio Interplanetario     |

| ISVR   | Instrument Science Verification Review              |

| NA     | Not Applicable                                      |

| OBS    | On-Board Software                                   |

| PA     | Product Assurance                                   |

| PACS   | Photoconductor Array Camera and Spectrometer        |

| PROM   | Programmable Read Only Memory                       |

| RAM    | Random Access Memory                                |

| SCC    | SpaceCraft Components                               |

| SEU    | Single Event Upset                                  |

| SPIRE  | Spectral and Photometric Imaging REceiver           |

| SVM    | Service Module                                      |

| SW     | Software                                            |

| TBC    | To Be Confirmed                                     |

| TBD    | To Be Defined                                       |

| TBW    | To Be Written                                       |

| TVT    | Thermal Vacuum Test                                 |

| - • -  |                                                     |

# **3** Subsystem Description

## 3.1 General Overview

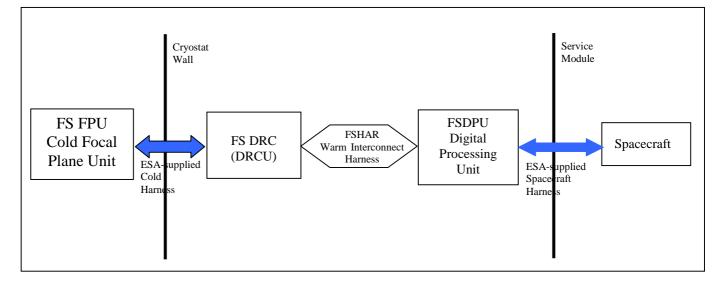

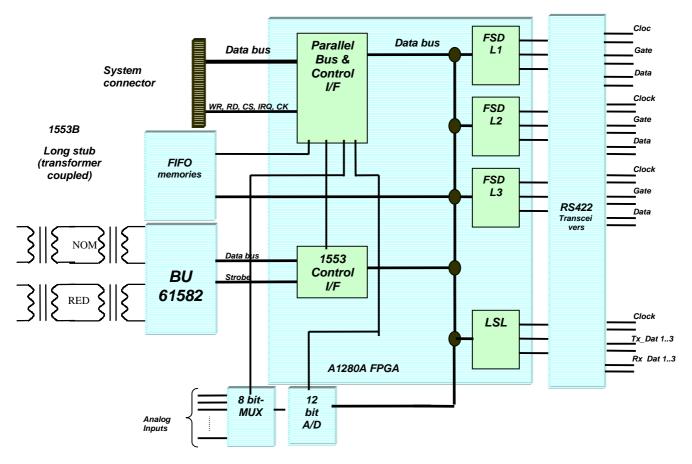

The DPU of the SPIRE Instrument (FSDPU) interfaces with the Detector readout and Control Unit subsystem (FSDRC) and with the S/C telemetry, telecommand (the on board CDMS, Command and Data Management system) and power systems. In Figure 3-1 the block diagram showing the interfaces of the FSDPU is presented, including the cryo-harness. Conceptually the FSDRC is a single unit. However for accomodation reasons it will be split into two physical units: Instrument Control Unit (FSICU) and Detector Readout Unit (FSDRU). FSICU contains:

- the electronics for the power conversion and distribution to the DRCU, for the control and readout of the thermometers, the cooler and the calibration sources (Subsystem Control Unit, SCU)

- the electronics for the control and readout of the cold mechanisms (Mechanisms Control Unit, MCU).

FSDRU contains the bias conditioning electronics for the bolometers arrays and JFET units and the lock in amplifiers and readout electronics for all the detector arrays.

Figure 3-1 SPIRE block diagram

The interface with FSDRC will be composed by three high speed data links for science data collection (two links with FSICU and one link with FSDRU) and one low speed serial bus with three output buffers, for command transmission and housekeeping data collection (two outputs to FSICU and one output to FSDRU). Refer to AD6 for a detailed description of the harness. The interface with the spacecraft shall be able to handle a baseline data rate of 100 kbps, with burst mode transmission up to 300 kbps. The interface shall be compliant with the MIL-STD-

DPU Subsystem Specification Document

Ref.:

SPIRE-IFS-PRJ-000462

Issue:

Issue 1.1

Date:

26/03/2001

Page:

Page 8 of 24

1553B standard, with the FSDPU acting as a remote terminal and the CDMS as the bus controller.

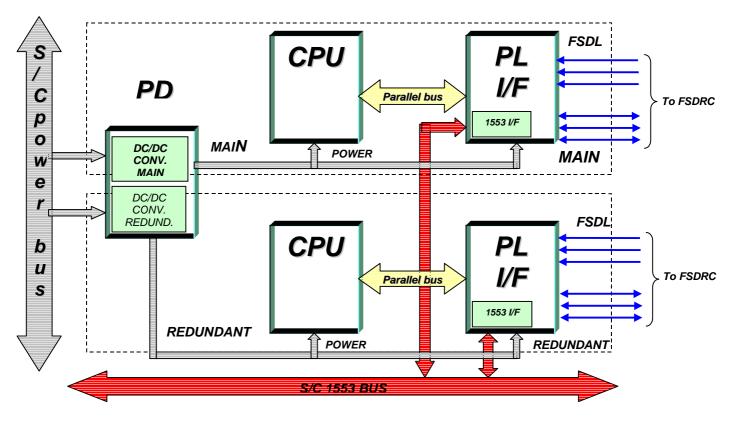

In Figure 3-2 the SPIRE DPU high level block diagram is shown: the FSDPU box is fully hardware redundant, with one DPU ON and the other in cold redundance. Each of the two redunded computers has its own DC/DC converter, CPU, memory and interfaces both to spacecraft and to the subsystems. Only the Avionic Models (see section 3.4) will have no redundancy, neither for the DC/DC converter, nor for the on board computer.

The main blocks of each of the two redunded DPUs are the CPU, the Spacecraft and subsystems interface and the DC/DC Converter.

Figure 3-2 FSDPU high level block diagram

## 3.2 Subsystem Design

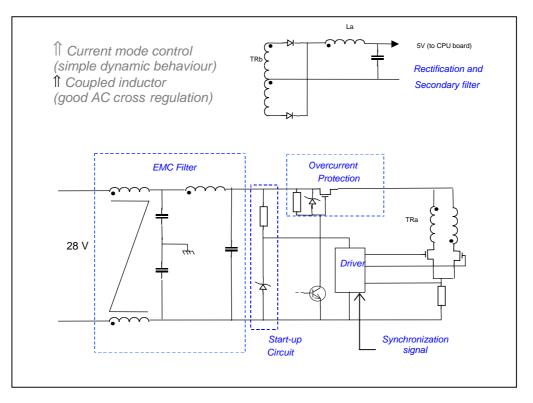

The FSDPU subsystem will include a synchronised DC/DC converter with a nominal input DC voltage of 28 V and the overall characteristics in agreement with AD2. In figure 3-3 a block diagram of the DC/DC converter is shown. Converter gets the redundant 131.072 kHz (TBC) synchronisation signal from the spacecraft. The synch signal is transformer coupled with the transformer located on the spacecraft. The receiver DPU interface shall have an impedance >05Kohm in parallel to <=2pF.

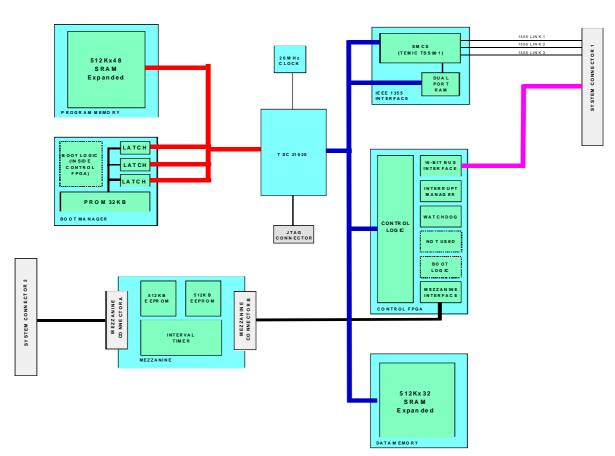

The adopted CPU is the TEMIC TSC21020, that is a Digital Signal Processor (DSP) unit developed by Analogue Devices and implemented for flight use by TEMIC.

The CPU board will be based on this chip (20 MHz clock), with:

- an appropriate timer for time management and synchronisation purposes

- a watch-dog system that can be hardware disabled through jumper;

- Rad Tolerant memories and components

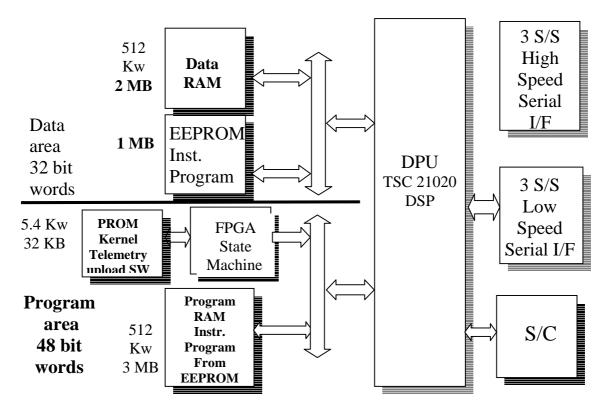

In Figure 3-4 the main blocks of the CPU board are shown.

Figure 3-3 DC/DC Converter scheme.

DPU Subsystem Specification Document

Ref.:

SPIRE-IFS-PRJ-000462

Issue:

Issue 1.1

Date:

26/03/2001

Page:

Page 10 of 24

Figure 3-5 CPU Board Block Diagram

**Document**

In Figure 3.4 the memory organisation of the CPU is shown with the dimensions of the various types of memories. The CPU board will carry (on the PROMs) some basic software containing at least:

- 1. a driver for the interface circuit with the S/C;

- 2. a programme loader through the S/C telemetry;

- 3. a driver for writing the EEPROMs;

- 4. a function to carry out the EEPROM checksum test.

The DPU interfaces mechanically with the S/C and electrically with the S/C and the various subsystems. The electrical hardware interface with the S/C consists in:

- interface with the S/C Power Distribution System and the 28 V lines;

- interface with the DC/DC synchronisation signal: 131.072 kHz (AD2, section 5.9.6.1) implemented through a transformer;

- interface with the telemetry and telecommand subsystems.

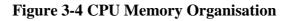

In figure 3-5 a block diagram of the S/C interface board is shown. The MIL-STD-1553B standard is implemented through one nominal and one redundant transformer in the long stub configuration.

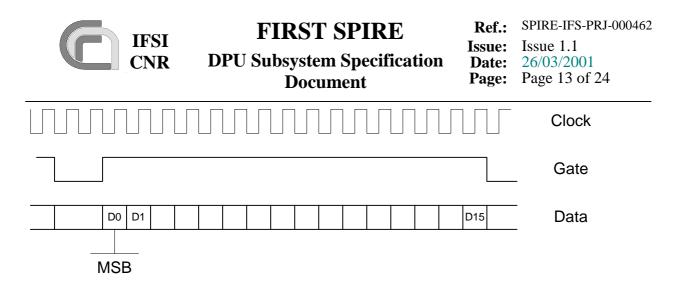

The interface between DPU and DRCU is shown schematically in Figure 3-7; a detailed description of this interface is given in RD1. For the science data link, **three monodirectional fast (1 MHz clock) synchronous serial input interfaces**, each of which with 8 KW 16 Bit FIFO, are foreseen: the data can be received by the DPU at the same time. The clock, gate and data signals, coming from the subsystems, are as in Figure 3-8.

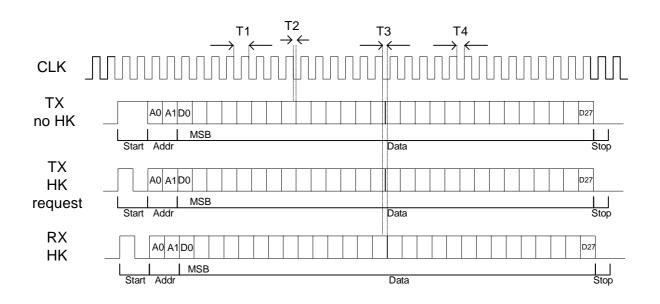

A serial synchronous bus is foreseen to interface with the control electronics of the focal plane unit subsystems: the bus will be used to transmit commands and receive responses or to control and receive housekeeping information. The baseline clock speed is 0.2 MHz (TBC). In Figure 3-9 the signals are shown: CLK & TX\_DAT are coming from DPU and go in parallel with three distinct hardware interfaces to the three DRCU electronics blocks; the three RX\_DAT lines are coming each from each of the three blocks and are multiplexed inside the DPU (see RD1).

DPU Subsystem Specification Document Document

Ref.:

SPIRE-IFS-PRJ-000462

Issue:

Issue 1.1

Date:

26/03/2001

Page:

Page 12 of 24

Figure 3-6 Spacecraft Interface Block Diagram

Figure 3-8 High speed interface protocol

#### Figure 3-10 FSDPU/FSDRCU Low Speed Interface protocol

All data transactions with the addressed subsystem (addr. In TX\_DAT), are initiated by DPU. DPU will send data to all subsystems using one serial data line TX\_DAT and can send both commands and HK requests via this line.

Subsystems, if required, will send responses via RX\_DAT line.

A command is made of 2 start bits, 2 address bits, 28 data bits and 1 stop bit.

A **HK request** is made by setting the second start bit.

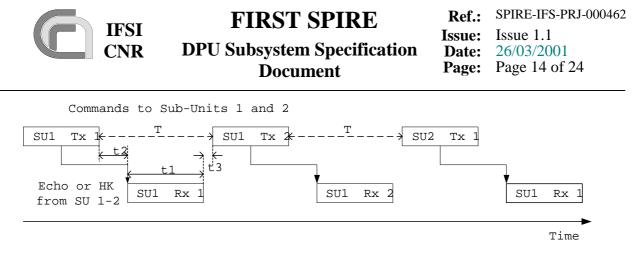

A **HK response** will consist of 2 start bits, 2 address bits, 28 data bits and 1 stop bit The sub-unit address field in the TX command is used to select the input channel RX. No command can be sent to a sub-unit until the echo/HK RX corresponding to the last command sent is received. Figure 3-10 shows the transmission-reception sequence.

#### Figure 3-10 Low speed Interface – transmission reception protocol

Clock and TX\_DAT are generated by DPU and distributed to all subsystems For internal reading of analogue signals an A/D converter (12 bit) plus MPX (8 Channels) will be provided in order to digitise the information of an internally conditioned thermistor and of the DC/DC converter voltage and total current.

## **3.3 Mission Profile**

The DPU will be designed to be used for 2 years on the ground, 2 years (TBC) of storage and 4 years in orbit with a probability better than 90% for the single ICU section (prime or redundant).

## **3.4 Product Tree**

The following deliverables are foreseen:

- DPU-AVM (Avionic Model): no redundancy, neither for the DC/DC converter, nor for the on board computer; only commercial grade components. These are to be used for the spire BBM (breadboard model), see section 2.4 of AD1. It is anticipated that it will not be possible to comply with what requested in AD2, chapter-page 9-1, paragraph 9.2.2.1, i.e. the AVM components will not be purchased, in general, from the same supplier of the FM/FS parts. The AVM will be delivered to ESA.

- 2) DPU-QM (Qualification Model): full redundancy, both for the DC/DC converter, and for the on board computer; only commercial grade components as far as possible within the fit, form and function of the flight model. The printed boards artwork will be the same as for FM/FS. This unit will undergo qualification tests. It is not a deliverable to ESA.

- 3) DPU-PFM (Proto-Flight Model ): full redundant box; SCC level B components for the spacecraft interface, SCC level C for all the other components is the baseline. If it is confirmed by ESA the decision to issue a Common Parts Procurement for which ESA will pay non recurring costs and surcharge costs, then in this case all components will be at SCC level B. This unit will undergo acceptance tests.

- 4) DPU-FS (Flight Spare): only spare boards (CPU, S/C I/F, SubSytem I/F, DC/DC Conv., mother board): SCC level B components for the spacecraft interface, SCC/C level for all the other components is the baseline, but the same as for the PFM applies. These boards will undergo acceptance tests.

FIRST SPIRE DPU Subsystem Specification

Ref.:

SPIRE-IFS-PRJ-000462

Issue:

Issue 1.1

Date:

26/03/2001

Page:

Page 15 of 24

#### Document

# 4 Specifications

## 4.1 Functional specifications

#### **4.1.1 Performance specifications**

| Requirement ID | Description                                                                                               | Reference      |

|----------------|-----------------------------------------------------------------------------------------------------------|----------------|

| DPU-FUN-01     | The interfaces of FSDPU with FSDRC shall be                                                               | RD2, AD4 Sect. |

|                | designed in order to couple with the maximum output                                                       | TBD            |

|                | <ul><li>data rates of the subsystems in the Cold Focal Plane:</li><li>FTS mechanism controller;</li></ul> |                |

|                | <ul> <li>Beam Steering Mirror;</li> </ul>                                                                 |                |

|                | <ul> <li>Detector Focal Planes units (3 Photometer arrays</li> </ul>                                      |                |

|                | and 2 Spectrometer arrays);                                                                               |                |

|                | - Sorption cooler;                                                                                        |                |

|                | - Temperature probes;                                                                                     |                |

|                | - DRU/ICU housekeeping;                                                                                   |                |

|                | - Calibration Sources.                                                                                    |                |

| DPU-FUN-02     | The DPU shall be able to acquire all Photometer                                                           | RD2, AD4 Sect. |

|                | detector pixels corresponding to a 4'x8' FOV (288                                                         | TBD            |

|                | detectors) at a maximum readout frequency of 40 Hz per                                                    |                |

|                | frame and 16 bits per sample.                                                                             |                |

| DPU-FUN-03     | The DPU shall be able to acquire all Spectrometer                                                         | RD2, AD4 Sect. |

|                | detector pixels corresponding to a 2.6'x2.6' FOV (56                                                      | TBD            |

|                | detectors) at a maximum readout frequency of 200 Hz                                                       |                |

|                | per frame and 16 bits per sample.                                                                         |                |

| DPU-FUN-04     | Photometer data: The instantaneous dynamic range of                                                       | AD4 Sect. TBD  |

|                | the readout of a pixel shall be 16 bits.                                                                  |                |

| DPU-FUN-05     | Spectrometer data: The instantaneous dynamic range of                                                     | AD4 Sect. TBD  |

|                | the readout of a pixel shall be: 15 bits (with background                                                 |                |

|                | nulling).                                                                                                 |                |

## **4.1.2** Technical specifications

| DPU-FUN-06 | The DPU shall be able to handle the adopted standard MIL-STD-1553B for the interface with the spacecraft, supporting an average telemetry rate of 96 kbps, when the instrument is in prime mode, and of 2 kbps otherwise. | AD2 sect. 5.11.1<br>AD3 sect. 5.11.1 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| DPU-FUN-07 | The DPU shall be able to handle the adopted standard MIL-STD-1553B for the interface with the spacecraft, supporting a maximum telecommand rate of 4 kbps.                                                                | AD2 sect. 5.11.4                     |

DPU Subsystem Specification Document

Ref.:

SPIRE-IFS-PRJ-000462

Issue:

Issue 1.1

Date:

26/03/2001

Page:

Page 16 of 24

| DPU-FUN-08 | Maximum DPU power consumption: 15W              | AD3 Sect. 5.9.3 |

|------------|-------------------------------------------------|-----------------|

|            | Note by IFSI: the actual estimate of the DPU HW |                 |

|            | manufacturer is $24\pm 6W$                      |                 |

## **4.2** Operational specifications

#### 4.2.1 Operational Safety

| Requirement ID | Description                                               | Reference    |

|----------------|-----------------------------------------------------------|--------------|

| DPU-SAF-01     | Failure of the DPU, or one of its components, shall not   | IRD-SAFE-R06 |

|                | affect the health of any other subsystem, the instrument  |              |

|                | or the interface with the satellite.                      |              |

| DPU-SAF-02     | Failure of any component in the DPU shall not damage      | IRD-SAFE-R09 |

|                | any redundant or backup component designed to replace     |              |

|                | that component in the subsystem                           |              |

| DPU- SAF-03    | No ASICs or FPGAs shall be capable of affecting           |              |

|                | instrument operations until they are in a defined state.  |              |

| DPU- SAF-04    | It shall be possible to break via software all electronic | IRD-REL-R05  |

|                | control loops implemented in hardware, provided that      |              |

|                | the relevant commands are implemented in the FSDRC        |              |

|                | in agreement with FSDPU.                                  |              |

| DPU- SAF-05    | The instrument shall monitor the operational status of    | IRD-AUT-R06  |

|                | the instrument on-board computer and take appropriate     |              |

|                | action in case of error. (a watchdog function will be     |              |

|                | implemented to identify if the on board computer has      |              |

|                | crashed) TBC                                              |              |

| DPU-SAF-06     | Cold redundant hardware shall be provided                 | IRD-REL-R03  |

#### 4.2.2 Lifetime

| Requirement ID | Description                                               | Reference |

|----------------|-----------------------------------------------------------|-----------|

| DPU-OPE-01     | The DPU PFM shall be designed to couple with an           | AD2       |

|                | integrated lifetime of 2 years.                           |           |

| DPU-OPE-02     | The DPU PFM shall be designed to couple with a            | AD2       |

|                | ground storage lifetime of 2 years (TBC).                 |           |

| DPU-OPE-03     | The DPU PFM shall be designed to couple with an in        | AD2       |

|                | orbit lifetime of 4 years, with a probability better than |           |

|                | 90% for the single DPU section (prime or redundant).      |           |

#### 4.2.3 Telemetry

The housekeeping parameters provided by the DPU are (list is TBC):

- DPU Voltage (2bytes)

- DPU Current (2bytes)

Ref.:

SPIRE-IFS-PRJ-000462

Issue:

Issue 1.1

Date:

26/03/2001

Page:

Page 17 of 24

• DPU Temperature (2bytes)

#### 4.2.4 Telecommands

The DPU dedicated commands are (list is TBC):

• DPU reset

command.

Command: DPU\_N\_Reset(); DPU\_R\_Reset() Parameters: Input --- None Output --- None

Action: Warm reset of the DPU. A warm reset is similar to a reboot without neither a memory test nor a copy of EEPROM into RAM. In this way the following DPU status is like after a switch-on but with its memory content preserved. *This is an immediate*

- Measurement Reset (TBC)

- Execute a function onboard Command: DPU\_N\_EXEC\_FUNCT (8,3) Parameters: Input --- FunctionID 8bits N 8bits PArameters NX16bits Action: Executes a function already stored onboard

- Set the telemetry rate Command: DPU\_N\_SET\_TM\_RATE (8,3) Parameters: Input --- mode 8bits Action: Set the telemetry rate: prime, parallel.

- Memory check

Command: DPU\_N\_MEM\_CHECK (6,9)

Parameters: Input --- MemID 8bits

Address 24bits

Length 16bits

Action: A checksum is derived for the specified are

Action: A checksum is derived for the specified area in memory.

• Memory load

Command: DPU\_N\_MEMORY\_LOAD (6,2)

Parameters: Input -- MemID

8bits

Address

24bits

Length

16bits

Data

16Xlength bits

Action: RAM Memory load (TBC)

Memory dump

Command: DPU\_N\_MEMORY\_DUMP (6,5)

Parameters: Input --- MemID 8bits

Address 24bits

**DPU Subsystem Specification**

Ref.:

SPIRE-IFS-PRJ-000462

Issue:

Issue 1.1

Date:

26/03/2001

Page:

Page 18 of 24

Document

16bits

Action: Memory dump applicable to any one of the 3 types of memory, PM, PM, EEPROM (TBC)

Subsystem Parameter Table Update Command: DPU\_N\_TABLE\_UPDATE (6,2) Parameters: Input Start 16 bit Length 16bit Data 16Xlength

Output --- Return 4 Bytes

Length

Action: The content at address Start is substituted for by the content at address Data. The pointers Start and Data are incremented by one an the operation is repeated until Length bytes have been transferred. This command updates (part of) the DPU parameters stored onboard in the *s ubsystems parameters table*. DATA are stored in Data memory starting from ADDRESS for a total of LENGTH bytes

• Set the predefined HK packet to be provided Command: DPU\_N\_SET\_HK\_LIST(8,3) Parameters: Input --- Mode 8bits Output --- Return 6 Bytes Result 1 Byte

Action: sets the predefined list of HK values for the HK packet (the total number of predefined packets depends on the number of operating modes).

• Enable packet transmission

Command: DPU\_N\_ENABLE\_PACKET\_TRANSMISSION(14,1)

Parameters: Input --- N

8bits

Type

8bits

Sub-type

8bits

SID

8bits

Action: enables the transmission of telemetry source packets of the specified type and subtype.

• Disable packet transmission

Command: DPU\_N\_DISABLE\_PACKET\_TRANSMISSION(14,2)

Parameters: Input

N

8bits

Type

8bits

Sub-type

8bits

SID

8bits

8bits

Action: disables the transmission of telemetry source packets of the specified type and subtype.

- All commands related to the time synchronisation (TBC): Command: DPU\_N\_TIME\_SYNC(9,4) Command: DPU\_N\_TIME\_VER(9,7) Command: DPU\_N\_TIME\_SET(9,4)

- Test connection(TBC)

**Command:** DPU\_N\_TEST\_CONN(17,1) **Action:** Start the "Are You alive?" procedure.

## **4.3 Interface Requirements**

The required operating temperatures at the interface of the SVM with FSDPU shall be compliant with AD3, section 5.7.3:

| Operating           |                     | Start-up       | Switch-off     | Non-ope             | erating             |

|---------------------|---------------------|----------------|----------------|---------------------|---------------------|

| Min. <sup>0</sup> C | Max. <sup>0</sup> C | <sup>0</sup> C | <sup>0</sup> C | Min. <sup>0</sup> C | Max. <sup>0</sup> C |

| -15                 | +45                 | -30            | +50            | -35                 | +60                 |

With acceptance temperature 5  ${}^{0}C$  below min. and 5  ${}^{0}C$  above max. operating temperatures. Qualification temperature 10  ${}^{0}C$  below min. and 10  ${}^{0}C$  above max. operating temperatures.

For what concerns the interfaces with the other instrument subsystems, the following requirement is applicable:

| Requirement ID | <b>Description</b> Reference                     |  |

|----------------|--------------------------------------------------|--|

| DPU-IF-01      | The interface with FSICU and FSDRU shall be IFSI |  |

|                | compliant with the description in AD6.           |  |

## 4.4 Design and Manufacturing Specifications

#### **4.4.1 Design requirements**

| Requirement ID | Description                                          | Reference |  |

|----------------|------------------------------------------------------|-----------|--|

|                | CPU board design                                     |           |  |

| DPU-DES-01     | The CPU board shall be based on the DSP TEMIC        | IFSI      |  |

|                | TSC21020, at least 20 MHz clock, chip.               |           |  |

| DPU-DES-02     | The CPU board shall carry a watch-dog system (TBC).  | IFSI      |  |

| DPU-DES-03     | The CPU board shall include a programmable timer,    | IFSI      |  |

|                | with a precision of 1 µs and a max capacity of 100s. |           |  |

| DPU-DES-04     | The CPU board shall have at least 32 kbytes of PROM  | IFSI      |  |

|                | memory with the bootstrap programme and software to  |           |  |

|                | face emergency situation and for maintenance.        |           |  |

| DPU-DES-05     | The CPU board shall have at least 512 Kbytes of      | IFSI      |  |

|                | EEPROM memory for the main programme.                |           |  |

| DPU-DES-06     | The CPU board should have at least 3 Mbytes of       | IFSI      |  |

|                | PROGRAMME static RAM.                                |           |  |

| DPU-DES-07     | The CPU board should have at least 2 Mbytes of       | IFSI      |  |

|                | DATA static RAM.                                     |           |  |

| DPU-DES-08     | It shall be possible to modify the EEPROM's content  |           |  |

|                | during flight through a maintenance programme        | IFSI      |  |

|                | resident in PROM and through a software programme    |           |  |

**Ref.:** SPIRE-IFS-PRJ-000462 **Issue:** Issue 1.1

#### **DPU Subsystem Specification** Document

**Date:** 26/03/2001 **Page:** Page 20 of 24

|            | a min a fram the tale common in the sector                                                                                                                                                                                                                                                                                                                                             |                    |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

|            | coming from the telecommand system.                                                                                                                                                                                                                                                                                                                                                    | TEOL               |

| DPU-DES-09 | All RAM (DRAM) memory (both DATA and PROGRAMME memory) should be SEU free.                                                                                                                                                                                                                                                                                                             | IFSI               |

| DPU-DES-10 | The CPU board shall have a system bus interface<br>working either in master or slave mode. In master mode<br>the board can have access to other digital boards<br>through the bus. In slave mode other master boards (for<br>instance the S/C interface board) can have access to a<br>Dual-Port RAM memory bank, accessible to CPU, to<br>exchange with CPU messages and data blocks. | IFSI               |

| DPU-DES-11 | <ul> <li>The CPU board shall carry on PROM the following basic software:</li> <li>a loader of a programme from telecommands;</li> <li>a driver for the spacecraft I/F (MIL-STD-1553B)</li> <li>a driver for the EEPROM writing.</li> <li>a function to carry out the EEPROM checksum test Moreover the CPU board shall support the EONIC Virtuoso operating system.</li> </ul>         |                    |

|            | Low speed interface design                                                                                                                                                                                                                                                                                                                                                             |                    |

| DPU-DES-12 | All links use the RS 422 standard (balanced line drivers and receivers).                                                                                                                                                                                                                                                                                                               | AD6 Sect. 4.1      |

| DPU-DES-13 | All the frequencies generated within the DPU shall<br>come from the same oscillator, in order to limit the<br>EMC problems.                                                                                                                                                                                                                                                            | AD1 Sect. 2.10     |

| DPU-DES-14 | All data transactions with any addressed subsystem<br>(addr. In TX_DAT, see fig. 3-9), are initiated by DPU.<br>DPU shall send data to all subsystems using one serial<br>bus line TX_DAT with three output buffers and can<br>send both commands and HK requests via this line.                                                                                                       | AD6 Sect. 4.2      |

| DPU-DES-15 | DPU shall be able to accept the subsystems responses via the three RX_DAT lines (see figure 3.7).                                                                                                                                                                                                                                                                                      | AD6 Sect. 4.2      |

| DPU-DES-16 | The Clock rate shall be at least 0.2MHz (TBC).                                                                                                                                                                                                                                                                                                                                         | IFSI               |

| DPU-DES-17 | Clock and TX_DAT shall be generated by DPU and distributed to all subsystems.                                                                                                                                                                                                                                                                                                          | AD6 Sect. 4.2, 4.5 |

| DPU-DES-18 | RX_DAT lines, coming from each subsystem, shall be multiplexed in the DPU.                                                                                                                                                                                                                                                                                                             | AD6 Sect. 4.2      |

| DPU-DES-19 | For internal reading of analogue signals an A/D<br>converter (12 bit) plus MPX (8 Channels) shall be<br>provided in order to digitise the information of an<br>internally conditioned thermistor and of the DC/DC<br>converter voltages and total DPU current.<br>High speed interface design                                                                                          | IFSI               |

| DPU-DES-20 | Three fast (1 MHz clock, TBC) synchronous serial<br>input interfaces shall be provided, each of which with 8<br>KW 32 Bit FIFO. The clock, gate and data signals,<br>coming from the subsystems, are as in Figure 2-8. All<br>data can be received by the DPU at the same time.                                                                                                        | AD6 Sect. 4.3      |

**Ref.:** SPIRE-IFS-PRJ-000462 **Issue:** Issue 1.1 **Date:** 26/03/2001

# DPU Subsystem Specification

Document

**Date:** 26/03/2001 **Page:** Page 21 of 24

| •                                                         | AD2 sect. 5.9.5.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| nominal is 28 V within 1%(TBC);                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| - max power to the DPU: 15W                               | AD3 sect. 5.9.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Note by IFSI: the actual estimate of the DPU HW           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| manufacturer is 24±6W                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| - efficiency of 70% or better;                            | IFSI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| - input filter with EMI-EMC properties (following ESA     | IFSI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| EMC/EMI specs);                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| - overall characteristics in agreement with FIRST IID-    | AD2 sect. 5.9.5.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| A (inrush current etc.).                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| - input impedance = $5$ kOhm in parallel to 200 pF.       | AD2 sect. 5.9.6.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| The DC/DC converter shall support a synchronisation       | AD2 sect. 5.9.6.1-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| signal (squarewave, 5.0 V +/- 20%, ground free,           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| transformer coupled) with a frequency of 131.073 kHz.     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Each of the two DC/DC converters shall be connected       | AD2 sect. 5.9.6.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| to an individual synchronisation signal                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                           | AD2 sect. 5.9.6.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| frequency +/- 10% with nominal performance.               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Spacecraft interface design                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| The spacecraft interface board shall be compliant with    | AD3 sect. 5.11.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| the MIL-STD-1553B standard.                               | AD2 sect. 5.11.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Overall mechanical design                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |